Pinout ak blòk dyagram nan kab la PL-USB2-Blaster

PL-USB2-Blaster a se yon eleman enpòtan nan FPGA Intel a Download seri kab, pèmèt konfigirasyon an nan Intel ® FPGAs atravè yon koneksyon USB.Atik sa a bay yon gade detaye nan konsepsyon li yo ak fonctionnalités, ki gen ladan pinout li yo, karakteristik, dyagram blòk, koneksyon, ak spesifik operasyonèl.Nou vize yo eksplore pa sèlman detay yo teknik nan aparèy la, men tou fasilite a ak efikasite li pote nan konfigirasyon FPGA.Katalòg

Ki sa ki se PL-USB2-Blaster a?

A PL-USB2-Blaster se yon eleman gwo nan Intel® FPGA Download seri kab la, fasilite transfè done efikas ant yon òdinatè ak yon FPGA nan yon koneksyon USB.Kab sa a amelyore prototip iteratif ak pwodiksyon pwogramasyon pa transmèt done konfigirasyon via yon estanda 10-PIN header sou yon tablo sikwi.Grasping fonksyonalite debaz yo nan PL-USB2-Blaster a se itilize pou deplwaman efikas li yo nan tout etap diferan nan devlopman FPGA.Aparèy sa a asire entegrasyon san pwoblèm nan anviwònman devlopman divès kalite, karakterize pa rapid ak konsistan kapasite transmisyon done li yo.

Pandan etap pwototip iteratif, presizyon ak ladrès yo bezwen.PL-USB2-BLASTER la sipòte uploading rapid nan konfigirasyon mete ajou, pèmèt tès rapid ak ajisteman nan dispozitif FPGA.Sa a ladrès se benefisye nan anviwònman ki nesesè iterasyon souvan nan amann-melodi desen ak san pèdi tan adrese pwoblèm.Konsistans nan pèfòmans yo mande nan pwogramasyon pwodiksyon an.PL-USB2-BLASTER garanti pwogramasyon egzat nan konfigirasyon final la nan FPGA a, asire fyab nan aplikasyon pou itilize fen.Sa a konsistans ede minimize dezakò ak amelyore efikasite, patikilyèman lè pwogram gwo komèsan nan inite.

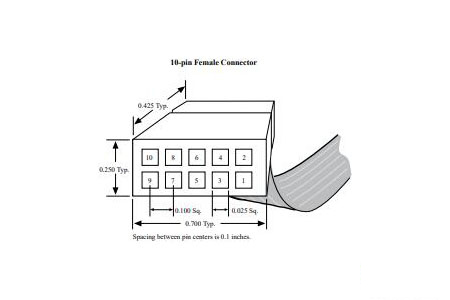

Pinout nan PL-USB2-Blaster

|

Nimewo PIN |

Non PIN |

Deskripsyon fonksyon |

|

1 |

Dcl |

PIN DCL la bon pou pwopagasyon siyal revèy la

pou operasyon synchronous.Li enpòtan pou minimize bri epi kenbe

Koneksyon ki estab ki sanble ak pratik konsepsyon wo-frekans sikwi. |

|

2 |

YD |

Ground (GND) sèvi kòm vòltaj la referans, asire

konsistan ak serye baz yo anpeche dezakò nan nivo siyal

ak bese pwoblèm tankou pasan tè. |

|

3 |

Conf_done |

PIN la conf_done endike fini an nan aparèy

konfigirasyon.Siveyans PIN sa a se itilize pou verifye siksè a

Inisyalizasyon nan periferik. |

|

4 |

VOCC (TRGT) |

PIN la VOCC founi pouvwa a sistèm nan sib, ak yon

Konsantre sou fournir vòltaj ki kòrèk la pou fè pou evite anba oswa sou-vòltaj

Kondisyon, itilize metòd règleman jesyon pouvwa. |

|

5 |

nconfig |

PIN la NCONFIG fasilite aparèy rkonfigurasyon sou

Aktivasyon, asire retabli oswa reprogramasyon reyalize san yo pa

entèripsyon. |

|

6 |

nce |

NCE (chip pèmèt) PIN kontwole eta a pèmèt nan

aparèy la, ki egzije bon deklarasyon pou aktive aparèy la lè sa nesesè,

analogue pou kontwole siyal pèmèt nan sikwi entegre. |

|

7 |

Doneout |

Dataout ki responsab pou pwodiksyon done yo, konsantre

sou transmisyon siyal pwòp pwoteje entegrite done ak enkòpore

Pwotokòl erè-tcheke kont koripsyon done. |

|

8 |

NCS |

PIN NCS (CHIP chwazi) aktive aparèy espesifik

konpozan, ak aktivasyon kontwole ak netralizasyon asire kòrèk la

Pati nan yon aparèy yo angaje nan moman yo dwa. |

|

9 |

Asdi |

ASDI yo itilize pou done opinyon, mete aksan sou bezwen an pou

Done egzak ak alè, senkronize opinyon menm jan ak sekans

Sikui lojik pou anpeche miscommunication. |

|

10 |

YD |

Menm jan ak PIN 2, PIN 10 bay yon lòt baz

pwen, konsantre sou mete ann aplikasyon plizyè pwen baz kòm yon estrateji

Komen nan sistèm segondè-presizyon amelyore estabilite ak pèfòmans. |

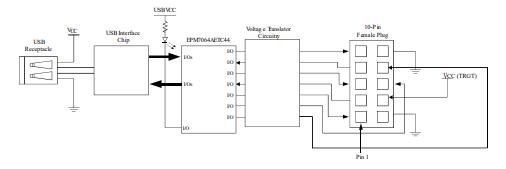

PL-USB2-BLASTER DIAGRAM fonksyonèl

Done routage ak chemen kominikasyon

Koòdone nan òdinatè lame sèvi kòm pwen inisyal la nan kontak pou done konfigirasyon.Aji kòm yon gwo kannal anba tè ant lojisyèl òdinatè a ak pyès ki nan konpitè PL-USB2-Blaster, koòdone sa a atache gwo vitès USB 2.0 pwotokòl fasilite rapid ak serye transmisyon done.Apre resepsyon done, inite a pwosesis nan PL-USB2-Blaster a sipoze kontwòl.Inite sa a, comprenant swa yon mikrokontroleur oswa FPGA, dilijans analiz, chèk pou erè, ak fòma done fèk ap rantre asire konpatibilite ak konpozan ki vin apre.

Post-pwosesis, done yo tanporèman loje nan inite tampon.Sa yo tanpon okipe distribisyon distribisyon ant gwo vitès done foul ak varye vitès pwosesis en.Pratik jesyon tanpon efikas yo bezwen, menm jan yo diminye entèripsyon ak pèt done.Pwochen etap la enplike nan transmèt done yo tampon nan FPGA a nan yon rezo ki defini aklè.Rezo sa a, ki enplike multiplexers, demultiplexers, ak chemen dedye, se fabrike prezève entegrite done ak senkronizasyon.Yon rezo routage ki byen aplike enpòtan;Suboptimal routage ka mennen nan erè konfigirasyon ak pwoblèm pèfòmans, jan yo note nan anpil aplikasyon pratik.

Senkronizasyon ak kontwòl distribisyon

Yon poto nan achitekti a se jenerasyon revèy la ak sistèm distribisyon, ki Worcester done transfere distribisyon asire operasyon san pwoblèm.Se presizyon nan distribisyon revèy souvan make pa lòt moun kòm itilize pou kenbe senkronizasyon ak pèfòmans optimal.Kenbe entegrite siyal la tou se yon eleman kle nan achitekti PL-USB2-Blaster la.Teknik tankou siyal diferans, matche enpedans, ak chemen pwoteje yo ap travay yo bese degradasyon siyal ak entèferans elektwomayetik (EMI).

Mekanism konfigirasyon avanse

Dyagram nan achitekti tou pentire mekanism pou deteksyon erè ak koreksyon.Teknik tankou chèk èkse siklik (CRC) ak lòt algoritm erè-deteksyon otomatikman idantifye ak korije dezakò kouran done, asire fyab la nan pwosesis la konfigirasyon.Metòd sa yo trè valè nan aplikasyon pou anpil pou wòl yo nan etabli sistèm gaya.Kapasite reconfiguration dinamik reprezante yon lòt karakteristik sofistike nan PL-USB2-Blaster la.Fonksyonalite sa a pèmèt pou modifikasyon konfigirasyon FPGA san yo pa kanpe operasyon yo, yon trè ekstrèmman valè nan senaryo kote adaptabilite ak minim D 'yo gen obligasyon.

Sèvi ak PL-USB2-Blaster

Enstalasyon chofè

Choute nan pwosesis la pa telechaje ak enstale Intel a bay chofè yo.Chofè sa yo sèvi kòm yon pon pou kominikasyon ant kab la ak aparèy informatique ou.Ou pral jwenn enstriksyon konplè nan pake a chofè, ofri yon gid etap-pa-etap nan enstalasyon an.

Koneksyon Materyèl

Apre enstale chofè yo, konekte kab PL-USB2-Blaster ki soti nan pò USB òdinatè w lan nan pò pwogramasyon aparèy sib la.Koneksyon sa a bon pou prepare konpozan pyès ki nan konpitè pou konfigirasyon kap vini an.

Lanse Quartus Prime Programmer

Dife moute Intel Quartus Premye lojisyèl an, tèt sou nan zouti nan 'pwogramè', epi chwazi dosye a konfigirasyon pyès ki nan konpitè.Koòdone zanmitay lojisyèl an asire yon pwosesis konfigirasyon senp, pèmèt ajisteman rapid ak konfigirasyon.

Fè konfigirasyon aparèy

Deplwaye pwogramè Quartus pou egzekite konfigirasyon aparèy la.Chwazi aparèy la sib nan lis la ak Upload dosye yo pwojè ki enpòtan.Inisye sekans nan pwogramasyon, ak lojisyèl an pral jere transfè a done, efektivman konfigirasyon aparèy FPGA ou.

Wòl siyal Tap la

Kab la PL-USB2-BLASTER pwolonje sipò nan siyal la TAP LOGIC analyzer, yon zouti pou analiz solid ki lojik.Siyal TAP ofri analiz lojik entegre, yon karakteristik pou debogaj ak verifye desen FPGA.

Mete kanpe siyal tiyo

Nan lojisyèl Quartus Pwemye a, configured siyal la Tap Lojik Analyzer pran ak egzaminen siyal yo.Pa defini kondisyon deklanche espesifik, ou ka délikatès kontwole koleksyon done, ede nan pinpointing pwoblèm nan konsepsyon an FPGA.

Itilizasyon abil nan kab PL-USB2-BLASTER mande yon men pwofon nan tou de pyès ki nan konpitè ak lojisyèl rèy.Entegre zouti sa yo nan pwosesis konsepsyon an pa kapab senplifye sik devlopman yo epi amelyore fyab pwodwi final la.Fusion nan konfigirasyon bon jan ak kapasite analyse vrèman ogmante efikasite nan devlopman FPGA.Konfòme yo ak direktiv sa yo ak swe karakteristik yo ki konplè nan PL-USB2-Blaster kab la ak Quartus Premye lojisyèl pèmèt yo navèt yon workflow devlopman gaya ak efikas, asire pèfòmans siperyè ak disponiblite nan desen FPGA yo.

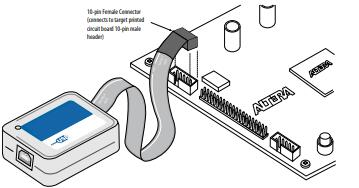

Kab-a-tablo koneksyon

Mezi sekirite pou operasyon an sekirite

Premye ak premye, asire w ke ou dekonekte tout sous pouvwa anvan ou kòmanse koneksyon an kab-a-tablo.Sa a prekosyon plak pwotèj kont danje elektrik ak pwoteje eleman yo delika sou tablo a aparèy.

Etabli koneksyon an

Kòmanse pa atache Intel FPGA Download kab la PC a.Kontinye konekte kab la nan header a 10-PIN sou tablo a aparèy.Apre verifye ke tout koneksyon yo an sekirite, retabli ekipman pou pouvwa a.Koneksyon sekirite ka evite erè done ak fasilite wout kominikasyon fò ant aparèy.

Enstale chofè a

Si sistèm lan siyal bezwen an pou nouvo enstalasyon chofè pyès ki nan konpitè, sòti nan sòsye inisyal la.Respekte direktiv enstalasyon manifakti a asire ke chofè ki apwopriye yo byen enstale.Apwòch sa a antreteni kapasite pi bon pèfòmans aparèy la.Atansyon Aderans a etap etap-pa-etap enstriksyon Intel a ka anpeche enstalasyon enkonplè ki ka rezilta nan pepen sistèm.

Detache kab la

Retire ekipman pou pouvwa a anvan deploge kab la yo anpeche nenpòt ki potansyèl domaj elektrik.Kontinye pa deploge kab la soti nan tablo a aparèy, ki te swiv pa dekonekte li soti nan PC a.Sekans nan dekoneksyon apwopriye ka bese risk mare nan pouvwa toudenkou.Apre yon pwosesis dekoneksyon sistematik sipòte lonjevite nan konpozan pyès ki nan konpitè epi yo ka lenmi depans reparasyon.

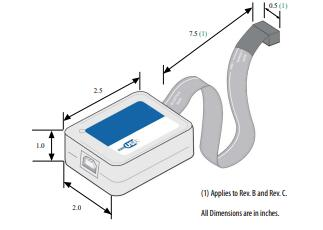

PL-USB2-BLASTER DIMENSIONS

Kesyon yo poze souvan [FAQ]

1. Ki objektif yon boutfeuz USB?

Yon boutfeu USB pèmèt itilizatè PC nan pwogram ak configured nan-sistèm aparèy via yon koneksyon USB.Zouti sa a rasyonalize pwosesis devlopman pou ou, fè li yon konpayon serye nan akitivite kreyatif ak teknik yo.

2. Kijan boutfeu USB a diferan de USB Blaster II a?

Blaster nan USB mwen sipòte sikwi JTAG ant 2.5V ak 3.3V.Nan contrast, USB boutfeu II a akeyir nan yon seri vòltaj pi laj soti nan 1.5V 5V epi li ofri karakteristik avanse.Adaptabilite nan USB boutfeu a II pèmèt pou konpatibilite ak yon varyete pi laj nan sistèm, agrandi itilizasyon li yo.Sa a adaptabilite amelyore fonctionnalités li yo, fè li yon zouti trè chache-apre nan senaryo pi konplèks.

3. Ki etap sa yo pou enstale yon chofè USB-Blaster?

Premyerman, konekte USB-Blaster a nan PC ou.Sou koneksyon, swiv sou ekran an envit yo chwazi opsyon enstalasyon chofè.Navige nan chofè yo ki sitiye nan anyè a enstalasyon Quartus Pwemye ak kontinye ak sòsye an enstalasyon jouk pwosesis la se konplètman ranpli.Metòd sa a senp asire entegrasyon san pwoblèm ak anviwònman devlopman ou.Fasilite nan pwosesis sa a pèmèt ou konsantre plis sou inovasyon ak kreyativite.

4. Ki sa ki condition ki nesesè pou lè l sèvi avèk Intel FPGA Download kab la?

Kòmanse pa enstale chofè ki apwopriye yo sou sistèm ou an.Premye etap sa a enpòtan.Imedyatman, configured pyès ki nan konpitè atravè Intel Quartus ® Premye lojisyèl an.Sa a preparasyon amann-melodi konfigirasyon ou pou pèfòmans optimal ak efikasite.

5. Ki sa ki Intel rekòmande pou pi bon pou sèvi ak Intel FPGA Download kab la?

Intel fòtman konseye lè l sèvi avèk vèsyon an ki pi resan nan Quartus Premye lojisyèl.Pa rete mete ajou ak dènye itérations yo, lòt moun jwenn aksè nan karakteristik ranfòse ak pèfòmans amelyore.Pratik sa a asire yon plis senplifye ak fè chak entèraksyon ak zouti a pi pwodiktif.