## Features

- 3.0V to 3.6V Read/Write

- Burst Read Performance

- ≤100 MHz (RAS Latency = 2, CAS Latency = 6), 10 ns Cycle Time t<sub>SAC</sub> = 7 ns

- ≤75 MHz (RAS Latency = 2, CAS Latency = 5), 13 ns Cycle Time t<sub>SAC</sub> = 8 ns

- <50 MHz (RAS Latency = 1, CAS Latency = 4), 20 ns Cycle Time t<sub>SAC</sub> = 9 ns

- MRS Cycle with Address Key Programs

- RAS Latency (1 and 2)

- CAS Latency (2 ~ 8)

- Burst Length: 4, 8

- Burst Type: Sequential and Interleaved

- Word Selectable Organization

- 16 (Word Mode)/x 32 (Double Word Mode)

- Sector Erase Architecture

- Eight 256K Word or 128K Double Word (4-Mbit) Sectors

- Independent Asynchronous Boot Block

- 8K x 16 Bits with Hardware Lockout

- Fast Program Time

- 3-volt, 100 µs per Word/Double Word Typical

- 12-volt, 30 µs per Word/Double Word Typical

- Fast Sector Erase Time

- 2.5 Seconds at 3 Volts

- 1.6 Seconds at 12 Volts

- Low-power Operation

- I<sub>CC</sub> Read = 75 mA Typical

- Input and Output Pin Continuity Test Mode Optimizes Off-board Programming

Package:

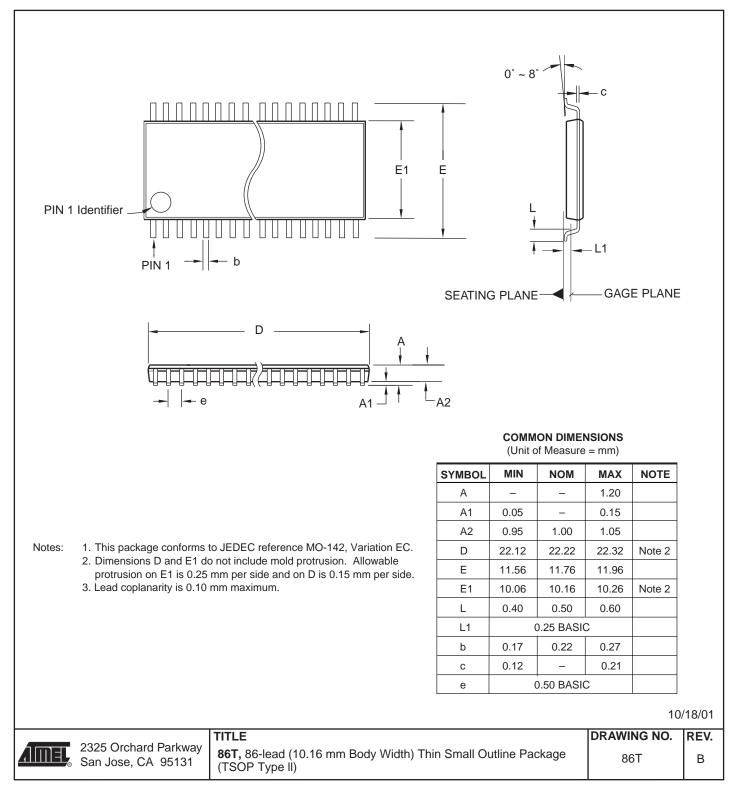

- 86-pin TSOP Type II with Off-center Parting Line (OCPL) for Improved Reliability

- LVTTL-compatible Inputs and Outputs

# Description

The AT49LD3200 or AT49LD3200B SFlash<sup>™</sup> is a synchronous, high-bandwidth Flash memory fabricated with Atmel's high-performance CMOS process technology and is organized either as 2,097,152 x 16 bits (word mode) or as 1,048,576 x 32 bits (double word mode), depending on the polarity of the WORD pin (see Pin Function Description Table). Synchronous design allows precise cycle control. I/O transactions are possible on every clock cycle. All operations are synchronized to the rising edge of the system clock. The range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high-bandwidth, high-performance memory system applications.

The AT49LD3200B will automatically activate the Asynchronous Boot Block after power-up, whereas with the AT49LD3200, the Asynchronous Boot Block can be activated through Mode Register Set.

The synchronous DRAM interface allows designers to maximize system performance while eliminating the need to shadow slow asynchronous Flash memory into high-speed RAM.

The 32-megabit SFlash device is designed to sit on the synchronous memory bus and operate alongside SDRAM.

32-megabit (1M x 32 or 2M x 16) High-speed Synchronous Flash Memory

AT49LD3200 AT49LD3200B SFlash<sup>™</sup>

To maximize system manufacturing throughput the AT49LD3200(B) features highspeed 12-volt program and erase options. Additionally, stand-alone programming cycle time of individual devices or modules is optimized with Atmel's unique input and output pin continuity test mode.

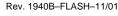

### **Pin Configuration**

<sup>2</sup> AT49LD3200(B)

# **Pin Function Description**

| Pin        | Name                     | Input Function                                                                                                                                                                                                                                                              |

|------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK        | System Clock             | Active on the rising edge to sample all inputs.                                                                                                                                                                                                                             |

| CS         | Chip Select              | Disables or enables device operation by masking or enabling all inputs except CLK and CKE.                                                                                                                                                                                  |

| CKE        | Clock Enable             | Masks system clock to freeze operation from the next clock cycle. CKE should be<br>enabled at least one cycle prior to new command. Disables input buffers for power-<br>down in standby mode.                                                                              |

| A0 - A12   | Address                  | Row/column addresses are multiplexed on the same pins.<br>Row address: $RA_0 \sim RA_{12}$ , Column address: $CA_0 \sim CA_6$ (x32), $CA_0 \sim CA_7$ (x16)                                                                                                                 |

| RAS        | Row Address Strobe       | Latches row addresses on the rising edge of the CLK with $\overline{\text{RAS}}$ low. Enables row access.                                                                                                                                                                   |

| CAS        | Column Address Strobe    | Latches column addresses on the rising edge of the CLK with $\overline{\text{CAS}}$ low. Enables column access.                                                                                                                                                             |

| MR         | Mode Register Set        | Enables mode register set with $\overline{\text{MR}}$ low. (Simultaneously $\overline{\text{CS}}$ , $\overline{\text{RAS}}$ and $\overline{\text{CAS}}$ are low).                                                                                                           |

| DQ0 - DQ31 | Data Input/Output        | Data input for program/erase. Data output for read.                                                                                                                                                                                                                         |

| VCC/VSS    | Power Supply/Ground      | Power and ground for the input buffers and the core logic.                                                                                                                                                                                                                  |

| VCCQ/VSSQ  | Data Output Power/Ground | Power and ground for the output buffers.                                                                                                                                                                                                                                    |

| WORD       | x32/x16 Mode Selection   | Double word mode/word mode, depending on polarity of $\overline{\text{WORD}}$ pin ( $\overline{\text{WORD}}$ = high, double word mode; $\overline{\text{WORD}}$ = low, word mode).<br>Should be set to the desired state during power-up and prior to any device operation. |

| DQM        | Data-out Masking         | Masks output operation when a complete burst is not required.                                                                                                                                                                                                               |

| NC         | No Connection            | Not connected                                                                                                                                                                                                                                                               |

| WE         | Write Enable             | Enables the chip to be written.                                                                                                                                                                                                                                             |

| VPP        | Program/Erase Pin Supply | Program/Erase power supply.                                                                                                                                                                                                                                                 |

# **Absolute Maximum Ratings\***

| Temperature under Bias                                                |

|-----------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                     |

| All Input Voltages<br>(including NC Pins)<br>with Respect to Ground   |

| All Output Voltages with Respect to Ground0.6V to $V_{\rm CC}$ + 0.6V |

| Voltage on V <sub>PP</sub><br>with Respect to Ground0.6V to +13.5V    |

| Power Dissipation 1 W                                                 |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

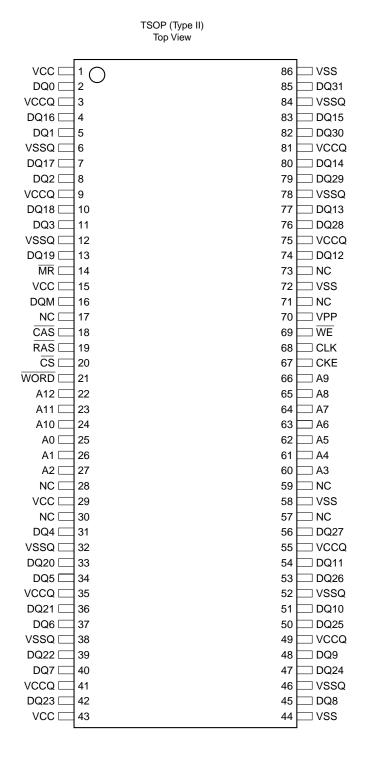

## **Functional Block Diagram**

# **DC and AC Operating Range**

|                                                 |            | AT49LD3200(B)-10 | AT49LD3200(B)-13 | AT49LD3200(B)-20 |

|-------------------------------------------------|------------|------------------|------------------|------------------|

| Operating Temperature                           | Commercial | 0°C - 70°C       | 0°C - 70°C       | 0°C - 70°C       |

| (Case)                                          | Industrial | -40°C - 85°C     | -40°C - 85°C     | -40°C - 85°C     |

| V <sub>CC</sub> , V <sub>CCQ</sub> Power Supply |            | 3.0V to 3.6V     | 3.0V to 3.6V     | 3.0V to 3.6V     |

# **DC Characteristics**

| Symbol           | Parameter                                              | Condition                                                     | Min  | Max                   | Units |

|------------------|--------------------------------------------------------|---------------------------------------------------------------|------|-----------------------|-------|

| I <sub>SB1</sub> | V <sub>CC</sub> Standby Current CMOS                   | CKE = 0, t <sub>CC</sub> = Min                                |      | 20                    | mA    |

| I <sub>SB2</sub> | V <sub>CC</sub> Standby Current TTL                    | $CKE \le V_{IL}$ (Max), $t_{CC} = Min$                        |      | 20                    | mA    |

| I <sub>SB3</sub> | V <sub>CC</sub> Active Standby Current                 | $\overline{CS} \ge V_{IH}$ (Min), t <sub>CC</sub> = Min       |      | 50                    | mA    |

| I <sub>cc</sub>  | V <sub>CC</sub> Active Current                         | t <sub>CC</sub> = Min, All Outputs Open                       |      | 150                   | mA    |

| I <sub>IL</sub>  | Input Leakage Current                                  | $0V \le V_{IN} \le V_{DD} + 0.3V$<br>Pins not under test = 0V | -10  | 10                    | μA    |

| I <sub>OL</sub>  | Output Leakage Current (IO <sub>OUT</sub><br>Disabled) | $(0V \le V_{OUT} \le V_{DD} Max)$<br>All Outputs in High-Z    | -10  | 10                    | μA    |

| V <sub>IH</sub>  | Input High Voltage, All Inputs                         | Note <sup>(1)</sup>                                           | 2.0  | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IL</sub>  | Input Low Voltage, All Inputs                          | Note <sup>(2)</sup>                                           | -0.3 | 0.8                   | V     |

| V <sub>OH</sub>  | Output High Voltage Level (Logic 1)                    | I <sub>OH</sub> = -2 mA                                       | 2.4  |                       | V     |

| V <sub>OL</sub>  | Output Low Voltage Level (Logic 0)                     | $I_{OL} = 2 \text{ mA}$                                       |      | 0.4                   | V     |

Notes: 1.  $V_{IH}$  (max) = 4.6V for pulse width <10 ns acceptable, pulse width measured at 50% of pulse amplitude.

2.  $V_{IL}$  (min) = -1.5V for pulse width <10 ns acceptable, pulse width measured at 50% of pulse amplitude.

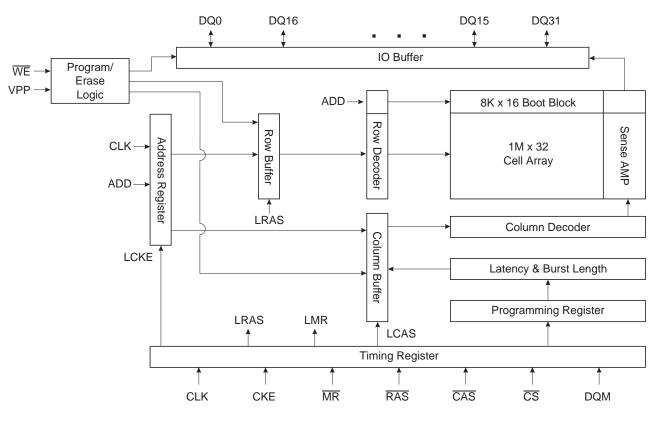

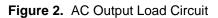

# **AC Operating Test Conditions**

$T_A = 0$  to 70°C,  $V_{CC} = 3.3V \pm 0.3V$ , unless otherwise noted.

| Parameter <sup>(1)</sup>                        | Value                                      |

|-------------------------------------------------|--------------------------------------------|

| Timing Reference Levels of Input/Output Signals | 1.4V                                       |

| Input Signal Levels                             | $V_{IH}/V_{IL} = 2.4V/0.4V$                |

| Transition Time (Rise & Fall) of Input Signals  | t <sub>r</sub> /t <sub>f</sub> = 1 ns/1 ns |

| Output Load                                     | LVTTL                                      |

Note: 1. If CLK transition time is longer than 1 ns, timing parameters should be compensated. Add [(t<sub>r</sub> + t<sub>f</sub>)/2-1] ns for transition time longer than 1 ns. Transition time is measured between V<sub>IL</sub> (max) and V<sub>IH</sub> (min).

Figure 1. DC Output Load Circuit

# Pin Capacitance<sup>(1)</sup>

f = 1 MHz, T = 25°C

| Symbol                          | Тур | Мах | Units | Conditions     |

|---------------------------------|-----|-----|-------|----------------|

| C <sub>IN</sub>                 | 4   | 6   | pF    | $V_{IN} = 0V$  |

| C <sub>OUT</sub> <sup>(2)</sup> | 8   | 12  | pF    | $V_{OUT} = 0V$ |

Notes: 1. This parameter is characterized and is not 100% tested.

2.  $V_{PP}$  behaves as an output pin.

# **AC Read Characteristics**

AC operating conditions unless otherwise noted.

|                   |                                                     | <u>&lt;</u> 100 | MHz | <u>&lt;</u> 75 | MHz | <u>&lt;</u> 50 | MHz |       |

|-------------------|-----------------------------------------------------|-----------------|-----|----------------|-----|----------------|-----|-------|

| Symbol            | Parameter                                           | Min             | Мах | Min            | Мах | Min            | Мах | Units |

| t <sub>CC</sub>   | CLK Cycle Time                                      | 10              |     | 13             |     | 20             |     | ns    |

| t <sub>SAC</sub>  | CLK to Valid Output Delay                           |                 | 7   |                | 8   |                | 9   | ns    |

| t <sub>OH</sub>   | Data Output Hold Time                               | 3               |     | 4              |     | 4              |     | ns    |

| t <sub>CH</sub>   | CLK High Pulse Width                                | 3               |     | 4              |     | 6.5            |     | ns    |

| t <sub>CL</sub>   | CLK Low Pulse Width                                 | 3               |     | 4              |     | 6.5            |     | ns    |

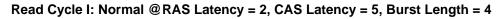

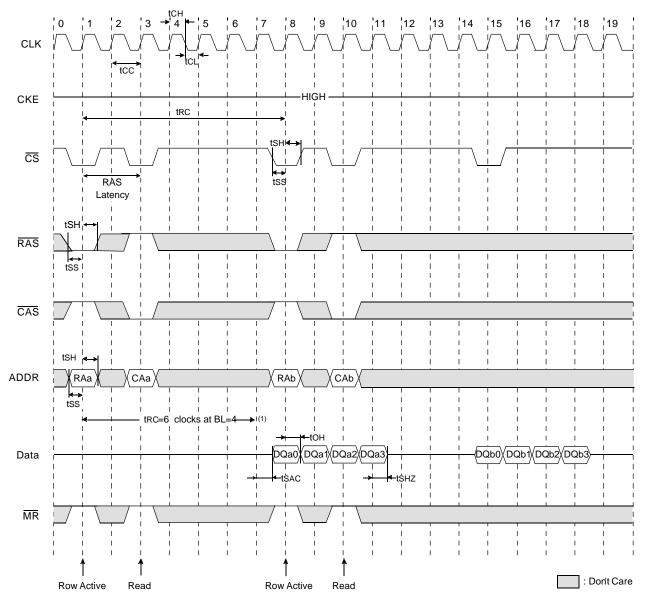

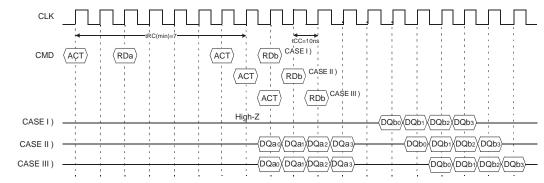

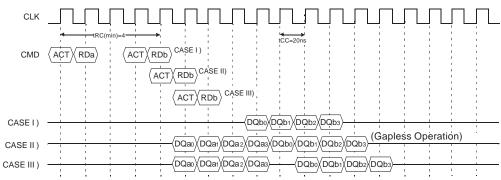

| t <sub>RC</sub>   | Row-active to Row-active <sup>(1)</sup>             | 11              |     | 10             |     | 9              |     | clks  |

| t <sub>SS</sub>   | Input Setup Time                                    | 2               |     | 4              |     | 4              |     | ns    |

| t <sub>SH</sub>   | Input Hold Time                                     | 1               |     | 2              |     | 2              |     | ns    |

| t <sub>SLZ</sub>  | CLK to Output in Low-Z                              | 0               |     | 0              |     | 0              |     | ns    |

| t <sub>SHZ</sub>  | CLK to Output in High-Z                             |                 | 7   |                | 10  |                | 15  | ns    |

| t <sub>T</sub>    | Transition Time                                     | 0.1             | 10  | 0.1            | 10  | 0.1            | 10  | ns    |

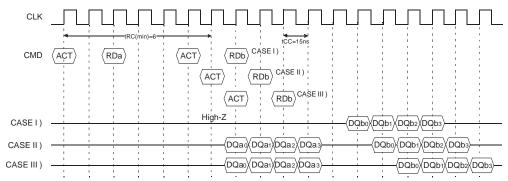

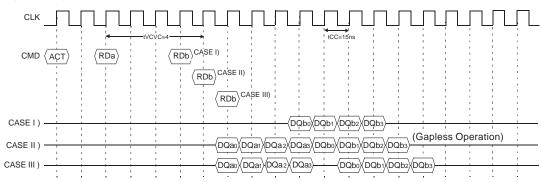

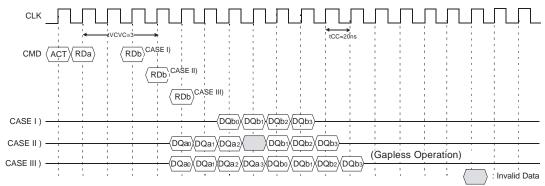

| t <sub>VCVC</sub> | Valid CAS Enable to Valid CAS Enable <sup>(2)</sup> | 9               |     | 8              |     | 7              |     | clks  |

Notes: 1. These  $t_{RC}$  values are for BL = 8. For BL = 4,  $t_{RC}$  = 7 CLKs for up to 100 MHz,  $t_{RC}$  = 6 CLKs for up to 75 MHz,  $t_{RC}$  = 5 CLKs for up to 50 MHz. RAS latency increase means a simultaneous  $t_{RC}$  increase in the same number of cycles. (If RAS latency is 3 CLKs,  $t_{RC}$  is 12 CLKs for BL = 8.) Refer to page 27 for gapless operation.

2. These  $t_{VCVC}$  values are for BL = 8. For BL = 4,  $t_{VCVC}$  = 5 CLKs for up to 100 MHz,  $t_{VCVC}$  = 4 CLKs for up to 75 MHz,  $t_{VCVC}$  = 3 CLKs for up to 50 MHz. Refer to page 27 for gapless operation.

## **Function Truth Table**

(V = Valid, X = Don't Care, H = Logic High, L = Logic Low)

Abbreviations (RA: Row Address, CA: Column Address, NOP: No Operation Command, DWM: Double Word Mode, WM: Word Mode)

| Command                     |                         |                          | CKEn-1 | CKEn | CS | RAS | CAS | <b>MR</b> <sup>(9)</sup> | DQM | Add.                | WORD | VPP | WE |

|-----------------------------|-------------------------|--------------------------|--------|------|----|-----|-----|--------------------------|-----|---------------------|------|-----|----|

| Register <sup>(1)</sup>     | Mode Reg                | ister Set                | Н      | Х    | L  | L   | L   | L                        | Х   | Code                | Х    | Х   | Х  |

| Row Active                  | Row Acces<br>& Latch    | SS                       | н      | Х    | L  | L   | Н   | н                        | х   | RA                  | x    | x   | х  |

| Read                        | Column Ac<br>& Latch    | Column Access<br>& Latch |        | Х    | L  | Н   | L   | н                        | х   | CA                  | х    | х   | н  |

|                             |                         | Н                        | Х      | L    | Н  | Н   | L   | Х                        | Х   | Х                   | Х    | Х   |    |

| Burst Stop                  | (Precharge<br>Synch. DR |                          | н      | Х    | L  | L   | Н   | L                        | х   | х                   | х    | х   | х  |

| Power-down                  | Two                     | Entry                    | Н      | L    | Х  | Х   | Х   | Х                        | Х   | Х                   | Х    | Х   | Х  |

| Suspend <sup>(2)</sup>      | Standby<br>Mode         | Exit                     | L      | Н    | Х  | Х   | х   | х                        | х   | Х                   | Х    | х   | Х  |

| DQM <sup>(3)</sup>          |                         |                          | Н      | Х    | Х  | Х   | Х   | Х                        | V   | х                   | х    | Х   | Х  |

|                             | .(4)                    |                          | Н      | Х    | н  | Х   | Х   | Х                        | Х   | х                   | х    | х   | Х  |

| No Operation Co             | ommand <sup>(4)</sup>   |                          | Н      | Х    | L  | Н   | Н   | Н                        | Х   | х                   | х    | Х   | Х  |

| 0 0                         | (5)                     |                          |        | Ň    |    |     |     |                          | X   | ~                   | н    | X   | н  |

| Organization Co             | ontrol                  |                          | Н      | Х    | L  | Н   | L   | Н                        | X   | CA                  | L    | Х   |    |

| Program/Erase <sup>(6</sup> | 6)                      |                          | Н      | Х    | L  | Н   | L   | Х                        | Х   | CA                  | х    | Х   | L  |

| Fast Program/E              | rase <sup>(6)</sup>     |                          | Н      | Х    | L  | Н   | L   | Х                        | Х   | CA                  | Х    | 12V | L  |

| Program/Erase               | Inhibit                 |                          | Н      | Х    | н  | Х   | Х   | Х                        | Х   | Х                   | х    | Х   | Х  |

| Product                     | Mode Reg                | ister Set                | Н      | Х    | L  | L   | L   | L                        | Х   | $A_7 = H$           | х    | Х   | Х  |

|                             | Read                    |                          | Н      | Х    | L  | Н   | L   | Н                        | Х   | L                   | х    | Х   | Н  |

|                             | Anda                    | Entry                    | Н      | Х    | L  | Н   | L   | Х                        | Х   | CA                  | х    | Х   | L  |

| Continuity Test N           | viode                   | Exit                     | Х      | Х    | Х  | Х   | Х   | Х                        | Х   | Code <sup>(8)</sup> | х    | Х   | Х  |

Notes: 1. A<sub>0</sub> ~ A<sub>6</sub>: Program keys (@MRS). After power-up, mode register set can be set before issuing other input command. After the Mode Register Set command is completed, no new commands can be issued for 3 CLK Cycles, and  $\overline{CS}$  or  $\overline{MR}$  state must be defined "H" within 3 CLK cycles. Refer to the Mode Register Control Table.

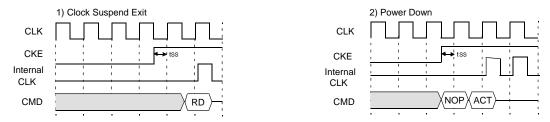

2. In the case CKE is low, two standby modes are possible. Those are standby mode in power-down, and active standby mode in clock suspend (non-power-down).

Power-down: CKE = "L" (after no command is issued for 60  $\mu$ s)

Clock Suspend: CKE = "L" (at the range of Row Active, Read and Data Out)

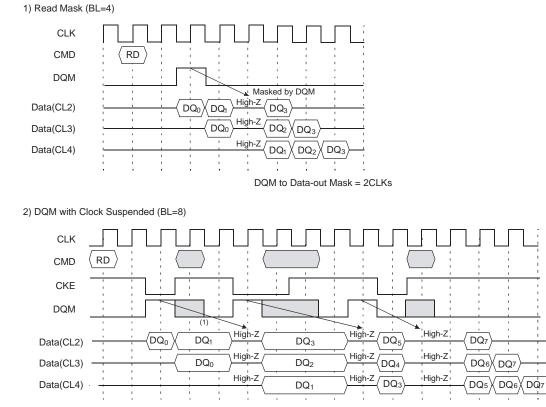

3. DQM sampled at rising edge of a CLK makes a high-Z state the data-out state, delayed by 2 CLK cycles.

4. Precharge command on Synch. DRAM can be used for Burst Stop operation during burst read operation only.

5. Mode selection is controlled by the polarity of WORD pin, "H" state is DWM, "L" state is WM. WORD should be set to the desired state during power-up and prior to any device operation.

- 6. Data is provided through  $DQ_0 \sim DQ_{31}$ . Refer to AC programming and erasing waveforms.

- 7.  $DQ_0 \sim DQ_{31}$  will output Manufacturer Code/Device Code.

- 8.  $A_0 = A_2 = A_{11} = "\underline{H}", A_1 = \underline{A}_{10} = A_{12} = "L"$

9. The user can tie MR and WE together to simplify the interface of the AT49LD3200(B) onto the standard SDRAM bus.

## **Asynchronous Boot Block Function Truth Table**

| Command                           | <b>CLK</b> <sup>(2)</sup> | <b>CKE</b> <sup>(2)</sup> | CS | RAS | CAS | MR | DQM | Add. | WORD | VPP | WE |

|-----------------------------------|---------------------------|---------------------------|----|-----|-----|----|-----|------|------|-----|----|

| Read                              | Х                         | Х                         | L  | Х   | Х   | Х  | L   | Add  | Х    | Х   | Х  |

| Output Disable                    | Х                         | Х                         | L  | Х   | Х   | Х  | Н   | Х    | Х    | Х   | Х  |

| Program/Erase <sup>(1)</sup>      |                           | Н                         | L  | Н   | L   | Х  | Х   | Add  | Х    | Х   | L  |

| Fast Program/Erase <sup>(1)</sup> |                           | Н                         | L  | Н   | L   | Х  | Х   | Add  | Х    | 12V | L  |

| Program/Erase Inhibit             |                           | Н                         | Н  | Х   | Х   | Х  | Х   | Х    | Х    | Х   | Х  |

Notes: 1. Program/Erase is performed through the synchronous bus cycle operation after the boot block is activated through either power-up or Mode Register Set.

2. It is recommended to hold CKE Low if CLK is running during asynchronous boot block mode except for synchronous command cycle and MRS operations.

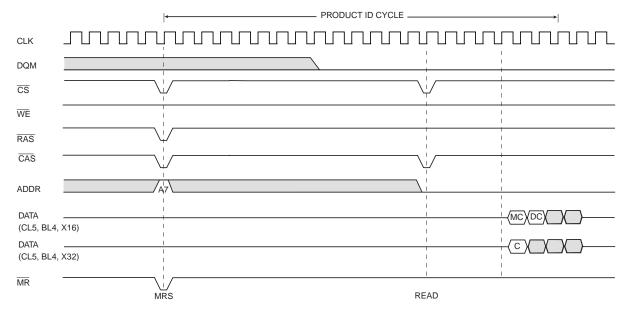

# Mode Register Control Table<sup>(1)</sup>

### **Register Programmed with MRS**

| Address  | A7 A6      |             | A5 A4 A3 |          | A2 | A1         | A0      |        |

|----------|------------|-------------|----------|----------|----|------------|---------|--------|

| Function | Product ID | RAS Latency | C/       | AS Laten | су | Burst Type | Burst I | Length |

| Prod | luct ID | RAS | Latency |    | CA | S Late | ency     |    | Burst Type |    | Burst Length |            |  |  |

|------|---------|-----|---------|----|----|--------|----------|----|------------|----|--------------|------------|--|--|

| A7   | "Read"  | A6  | Туре    | A5 | A4 | A3     | Length   | A2 | Туре       | A1 | A0           | Length     |  |  |

| 0    | Array   | 0   | 1       | 0  | 0  | 0      | Reserved | 0  | Sequential | 0  | 0            | Reserved   |  |  |

| 1    | ID      | 1   | 2       | 0  | 0  | 1      | 2        | 1  | Interleave | 0  | 1            | 4          |  |  |

|      |         |     |         | 0  | 1  | 0      | 3        |    |            | 1  | 0            | 8          |  |  |

|      |         |     |         | 0  | 1  | 1      | 4        |    |            | 1  | 1            | Boot Block |  |  |

|      |         |     |         | 1  | 0  | 0      | 5        |    |            |    |              |            |  |  |

|      |         |     |         | 1  | 0  | 1      | 6        |    |            |    |              |            |  |  |

|      |         |     |         | 1  | 1  | 0      | 7        | 1  |            |    |              |            |  |  |

|      |         |     |         | 1  | 1  | 1      | 8        | 1  |            |    |              |            |  |  |

Note: 1. After power-up, when the user wants to change Mode Register Set, the user must exit from power-down mode and start Mode Register Set before entering normal operation mode. Reserved modes are not to be used; device function in these modes is not guaranteed.

# **Addressing Map**

### WORD = "H": x32 Organization<sup>(1)</sup>

| Function       | A <sub>0</sub> | A <sub>1</sub>  | A <sub>2</sub>  | A <sub>3</sub> | A <sub>4</sub> | $A_5$  | $A_6$                          | A <sub>7</sub>  | A <sub>8</sub>  | A <sub>9</sub> | A <sub>10</sub>  | A <sub>11</sub>  | A <sub>12</sub>  |

|----------------|----------------|-----------------|-----------------|----------------|----------------|--------|--------------------------------|-----------------|-----------------|----------------|------------------|------------------|------------------|

| Row Address    | $RA_0$         | RA <sub>1</sub> | $RA_2$          | $RA_3$         | $RA_4$         | $RA_5$ | $RA_6$                         | RA <sub>7</sub> | RA <sub>8</sub> | $RA_9$         | RA <sub>10</sub> | RA <sub>11</sub> | RA <sub>12</sub> |

| Column Address | $CA_0$         | CA <sub>1</sub> | CA <sub>2</sub> | $CA_3$         | $CA_4$         | $CA_5$ | CA <sub>6</sub> <sup>(1)</sup> | Х               | Х               | Х              | Х                | Х                | Х                |

Note: 1. Column Address MSB (at x32 organization) (X = Don't Care)

### WORD = "L": x16 Organization<sup>(1)</sup>

| Function       | A <sub>0</sub>  | A <sub>1</sub>  | $A_2$  | $A_3$  | A <sub>4</sub>  | $A_5$  | A <sub>6</sub> | A <sub>7</sub>                 | A <sub>8</sub> | A <sub>9</sub> | A <sub>10</sub>  | A <sub>11</sub>  | A <sub>12</sub>  |

|----------------|-----------------|-----------------|--------|--------|-----------------|--------|----------------|--------------------------------|----------------|----------------|------------------|------------------|------------------|

| Row Address    | $RA_0$          | $RA_1$          | $RA_2$ | $RA_3$ | $RA_4$          | $RA_5$ | $RA_6$         | RA <sub>7</sub>                | $RA_8$         | $RA_9$         | RA <sub>10</sub> | RA <sub>11</sub> | RA <sub>12</sub> |

| Column Address | CA <sub>0</sub> | CA <sub>1</sub> | $CA_2$ | $CA_3$ | CA <sub>4</sub> | $CA_5$ | $CA_6$         | CA <sub>7</sub> <sup>(1)</sup> | Х              | Х              | Х                | Х                | Х                |

Note: 1. Column Address MSB (at x16 organization) (X = Don't Care)

### Each Address is Arranged as Follows<sup>(1)(2)</sup>

For X32 operation,

|                  | MSB              |                  |                  |                     |                 |        |   |                 |                 |                 | LSB             |

|------------------|------------------|------------------|------------------|---------------------|-----------------|--------|---|-----------------|-----------------|-----------------|-----------------|

| Address Register | AR <sub>19</sub> | AR <sub>18</sub> | AR <sub>17</sub> | <br>AR <sub>8</sub> | AR <sub>7</sub> | $AR_6$ |   | AR <sub>3</sub> | AR <sub>2</sub> | AR <sub>1</sub> | AR <sub>0</sub> |

| Address          | RA <sub>12</sub> | RA <sub>11</sub> | RA <sub>10</sub> | <br>RA <sub>1</sub> | RA <sub>0</sub> | $CA_6$ |   | $CA_3$          | CA <sub>2</sub> | CA <sub>1</sub> | CA <sub>0</sub> |

|                  |                  |                  |                  |                     |                 |        |   |                 |                 | BL              | = 4             |

|                  |                  |                  |                  |                     |                 |        | * | nitial Addı     | ess B           | L = 8           |                 |

Notes: 1. For X16 operation, when  $CA_0$  is set to Low, data belonging to 0 ~ 15th registers are output to  $DQ_0 \sim DQ_{15}$  pins, and when  $CA_0$  is set to High, data belonging to 16 ~ 31th registers are output to  $DQ_0 \sim DQ_{15}$  pins.

2. Asynchronous Boot Block uses x16 operation and  $A_0 \sim A_{12}$  as address inputs.

# Burst Sequence (Burst Length = 4)

| Initial A | Address |   |      |        |   |            |   |   |   |  |  |

|-----------|---------|---|------|--------|---|------------|---|---|---|--|--|

| A1        | A0      |   | Sequ | ential |   | Interleave |   |   |   |  |  |

| 0         | 0       | 0 | 1    | 2      | 3 | 0          | 1 | 2 | 3 |  |  |

| 0         | 1       | 1 | 2    | 3      | 0 | 1          | 0 | 3 | 2 |  |  |

| 1         | 0       | 2 | 3    | 0      | 1 | 2          | 3 | 0 | 1 |  |  |

| 1         | 1       | 3 | 0    | 1      | 2 | 3          | 2 | 1 | 0 |  |  |

# **Burst Sequence (Burst Length = 8)**

| In | itial Addre | SS |   |            |   |   |   |   |   |   |   |            |   |   |   |   |   |   |

|----|-------------|----|---|------------|---|---|---|---|---|---|---|------------|---|---|---|---|---|---|

| A2 | A1          | A0 |   | Sequential |   |   |   |   |   |   |   | Interleave |   |   |   |   |   |   |

| 0  | 0           | 0  | 0 | 1          | 2 | 3 | 4 | 5 | 6 | 7 | 0 | 1          | 2 | 3 | 4 | 5 | 6 | 7 |

| 0  | 0           | 1  | 1 | 2          | 3 | 4 | 5 | 6 | 7 | 0 | 1 | 0          | 3 | 2 | 5 | 4 | 7 | 6 |

| 0  | 1           | 0  | 2 | 3          | 4 | 5 | 6 | 7 | 0 | 1 | 2 | 3          | 0 | 1 | 6 | 7 | 4 | 5 |

| 0  | 1           | 1  | 3 | 4          | 5 | 6 | 7 | 0 | 1 | 2 | 3 | 2          | 1 | 0 | 7 | 6 | 5 | 4 |

| 1  | 0           | 0  | 4 | 5          | 6 | 7 | 0 | 1 | 2 | 3 | 4 | 5          | 6 | 7 | 0 | 1 | 2 | 3 |

| 1  | 0           | 1  | 5 | 6          | 7 | 0 | 1 | 2 | 3 | 4 | 5 | 4          | 7 | 6 | 1 | 0 | 3 | 2 |

| 1  | 1           | 0  | 6 | 7          | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7          | 4 | 5 | 2 | 3 | 0 | 1 |

| 1  | 1           | 1  | 7 | 0          | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

## **Device Operations**

Clock (CLK)

A square wave signal (CLK) must be applied externally at cycle time  $t_{CC}$ . All operations are synchronized to the rising edge of the clock. The clock transitions must be monotonic between  $V_{IL}$  and  $V_{IH}$ . During operation with CKE high, all inputs are assumed to be in valid state (low or high) for the duration of setup and hold time around the positive edge of the clock for proper functionality and  $I_{CC}$  specifications.

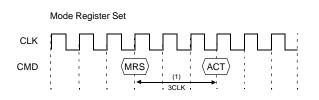

- **Clock Enable (CKE)** The clock enable (CKE) gates the clock into the AT49LD3200(B) and is asserted high during all cycles, except for power-down, standby and clock suspend mode. If CKE goes low synchronously with clock (setup and hold time same as other inputs), the internal clock is suspended from the next clock cycle and the state of output and burst address is frozen for as long as the CKE remains low. All other inputs are ignored from the next clock cycle after CKE goes low. The AT49LD3200(B) remains in the power-down mode, ignoring other inputs for as long as CKE remains low. The power-down exit is synchronous as the internal clock is suspended. When CKE goes high at least "1 CLK + t<sub>SS</sub>" before the rising edge of the clock, then the AT49LD3200 becomes active from the same clock edge accepting all the input commands.

- NOP and DeviceWhen RAS, CAS and MR are high, the AT49LD3200(B) performs no operation (NOP).DeselectNOP does not initiate any new operation. Device deselect is also a NOP and is entered<br/>by asserting CS high. CS high disables the command decoder so that RAS, CAS, MR

|                         | and all the address inputs are ignored. In addition, entering a Mode Register Set com-<br>mand in the middle of a normal operation results in an illegal state in the<br>AT49LD3200(B).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-up                | <ol> <li>The following power-up sequence is recommended.</li> <li>Apply power and start clock. Hold the MR, CKE and DQM inputs high; all other pins are a NOP condition at the inputs before or along with V<sub>CC</sub> (and V<sub>CCQ</sub>) supply.</li> <li>Set WORD to the desired state (prior to any device operation).</li> <li>To change the default Mode Register Set values, perform a Mode Register Set cycle to program the RAS latency, CAS latency, burst length and burst type.</li> <li>At the end of three clock cycles after the mode register set cycle, the device is ready for operation.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                         | When the above sequence is used for power-up, all outputs will be in high impedance state. The high impedance of outputs is not guaranteed in any other power-up sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                         | For AT49LD3200B, Asynchronous Boot Block will be selected after power-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Mode Selection Control  | Mode selection is controlled by the polarity of WORD pin. WORD should be set to the desired state during power-up and prior to any device operation. The AT49LD3200(B) can be organized as either double word wide (x32) or word wide (x16). The organization is selected via the WORD pin. When WORD is asserted high (V <sub>IH</sub> ), the double word-wide organization is selected. When WORD is asserted low (V <sub>IL</sub> ), the word-wide organization is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Address Decoding        | The address bits required to decode one of the available cell locations out of the total depth are multiplexed onto the address select pins and latched by externally applying two commands. The first command, $\overline{RAS}$ asserted low, latches the row address into the device. A second command, $\overline{CAS}$ asserted low, subsequently latches the column address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

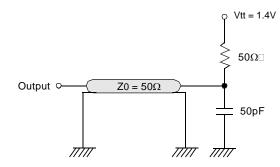

| Mode Register Set (MRS) | The mode register stores the data for controlling the various operating modes of AT49LD3200(B). It programs the RAS latency, CAS latency, burst length, burst type, selects product ID Read or activates the Asynchronous Boot Block. For AT49LD3200(B), the default value of the mode register is defined as array read with RAS latency = 2, CAS latency = 5, burst length = 4, sequential burst type. When and if the user wants to change its values, the user must exit from power-down mode and start Mode Register Set before entering normal operation mode. The mode register is reprogrammed by asserting low on $\overline{CS}$ , RAS, CAS and MR (the AT49LD3200(B) should be in active mode with CKE already high prior to writing the mode register). The state of address pins $A_0 \sim A_7$ in the same cycle as $\overline{CS}$ , RAS, CAS and MR going low is the data written in the mode register. Three clock cycles are required to complete the program in the mode register is divided into various fields, depending on functionality. The burst length field uses $A_0 \sim A_1$ , burst type uses $A_2$ , CAS latency (read latency from column address) uses $A_3 \sim A_5$ , RAS latency uses $A_6$ (RAS to CAS delay), array read or product ID read uses A7. Refer to Mode Register Control Table for specific codes for various burst lengths, burst types, CAS latencies, RAS latencies, and read modes. |

AMEL

| Latency                         | There are latencies between the issuance of a Row Active command and when data is available on the I/O buffers. The RAS to CAS delay is defined as the RAS latency. The CAS to data out delay is the CAS latency. The CAS and RAS latencies are programmable through the mode register. RAS latencies of 1 and 2, and CAS latencies of 2 through 6 are supported. It is understood that some RAS and CAS latency values are reserved for future use, and are not available in this generation of synchronous Flash. The following are the supported minimum values: RAS latency = 2, and CAS latency = 6 for 100 MHz operation, and RAS latency = 2, and CAS latency = 5 for 66 MHz operation, and RAS latency = 1, and CAS latency = 4 for 50 MHz operation, and RAS latency = 1, and CAS latency = 3 for 33 MHz operation. |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

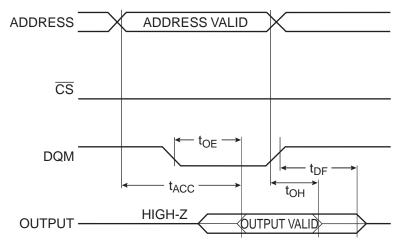

| DQM Operation                   | The DQM is used to mask output operations when a complete burst read is not required. It works similar to $\overline{OE}$ during a read operation. The read latency is two cycles from DQM, which means DQM masking occurs two cycles later in the read cycle. DQM operation is synchronous with the clock. The masking occurs for a complete cycle. (Also refer to the DQM timing diagram.)                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Burst Read                      | The Burst Read command is used to access a burst of data on consecutive clock cycles from an active row state. The Burst Read command is issued by asserting low CS and CAS with MR being high on the rising edge of the clock. The first output appears in CAS latency number of clock cycles after the issuance of the Burst Read command. The burst length, burst sequence and latency from the Burst Read command are determined by the mode register, which is already programmed. Burst read can be initiated on any column address of the active row. The output goes into high-impedance at the end of the burst, unless a new burst read is initiated to keep the data output gapless. The burst read can be terminated by issuing another burst read.                                                              |

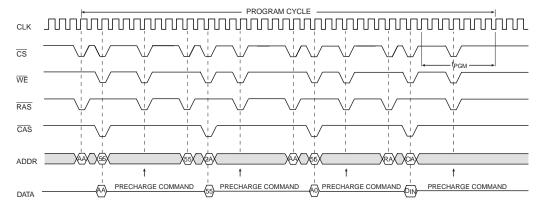

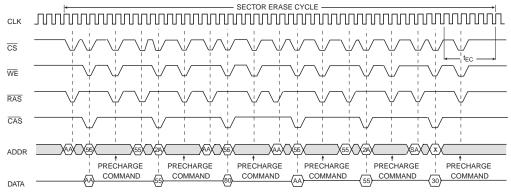

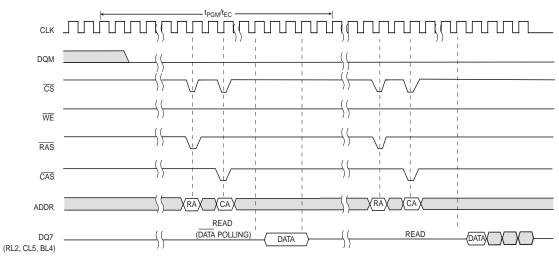

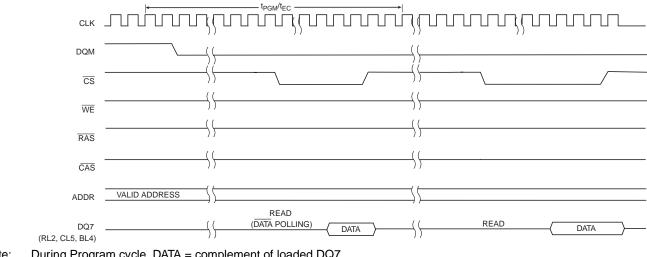

| Sector Erase                    | Before a word/double word can be reprogrammed, it must be erased. The erased state of the memory bits is a logical "1". The AT49LD3200(B) is organized into eight uniform four megabit sectors (SA0 - SA7) that can be individually erased. The Sector Erase command is a synchronous six-bus cycle operation (refer to the Command Definition table and Program Cycle and Erase Cycle waveforms). The erase code consists of 6-byte (DQ8 - DQ31 are Don't Care inputs for the command) load commands to specific address locations with a specific data pattern. The sector address and 30H data input are latched in the sixth cycle. The sector erase starts at the following rising edge of CLK after the sixth cycle. The erase operation is internally controlled; it will automatically time to completion.           |

|                                 | Any commands written to the device during the erase cycle will be ignored. The maximum time needed to erase one sector is $t_{\rm EC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Word/Double Word<br>Programming | Once a sector is erased, it is programmed (to a logical "0") on a word-by-word/double-<br>word-by-double-word basis. Programming is accomplished via the internal device com-<br>mand register and is synchronous four-bus cycle operation (refer to the Command<br>Definition table and Program Cycle and Erase Cycle waveforms). The programming<br>operation starts at the following rising edge of CLK after the fourth cycle. The device will<br>automatically generate the required internal program pulses.<br>Any commands written to the device during the embedded programming cycle will be<br>ignored. Please note that a data "0" cannot be programmed back to a "1"; only erase                                                                                                                                |

|                                 | operations can convert "0"s to "1"s. Programming is completed after the specified $t_{PGM}$ cycle time. The DATA polling feature may also be used to indicate the end of a program cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|  | EL  |

|--|-----|

|  | - R |

|  |     |

| Product Identification      | The product identification mode identifies the device and manufacturer as Atmel. This mode can be used by an on-board controller or external programmer to identify the correct programming algorithm for the Atmel product.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA Polling                | The AT49LD3200(B) features DATA polling to indicate the end of a program or sector erase cycle. DATA polling may begin at any time during the program or sector erase cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                             | During a program cycle, an attempted read of the last word/double word loaded will result in the complement of the loaded data in DQ7. Once the program cycle has completed, true valid data can be read on all outputs and the next cycle may begin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                             | During a sector erase operation, an attempt to read the device will give a "0" on DQ7.<br>Once the sector erase cycle has completed, logical "1" data can be read on all outputs<br>from the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Hardware Data<br>Protection | Hardware features protect against inadvertent programming or erasure to the AT49LD3200(B) in the following way: $V_{CC}$ sense: if $V_{CC}$ is below 2.3V (typical), the program or erase function is inhibited; but if $V_{CC}$ dips below 2.3V during program or erase cycle, the respective function will be interrupted and the data at the location being programmed may be corrupted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

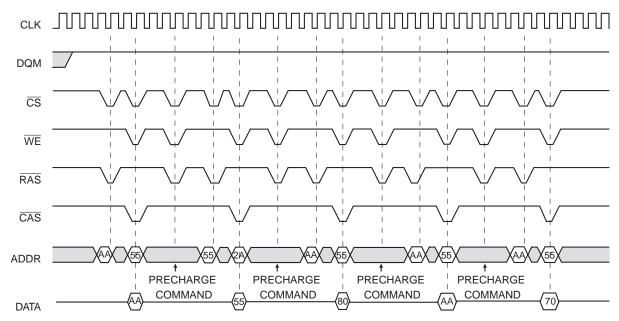

| Continuity Test Mode        | The AT49LD3200(B) has built-in circuitries to make input and output pin continuity check simple and easy. This mode can be activated via the internal device command register and is a synchronous five-bus cycle operation (refer to the Command Definition Table and Continuity Test Mode Entry Waveforms). After the bus cycle operation, keep DQM high (V <sub>IH</sub> ) and allow 5 µsec for circuit setup time or until data is no longer asserted at DQ0 - DQ7, whichever takes longer. This will keep DQ0 - DQ7 from contention since data is asserted at DQ0 - DQ7 during the mode entry sequence. Then DQM can be asserted low (V <sub>IL</sub> ) to enable DQ0 - DQ7 for test. Once in this asynchronous mode, input pins are virtually tied to output pins internally forming input - output pin pairs. The output pin of the pair will follow the logic state of the input pin of the pair (refer to the Input - Output Pin Pairs table). To exit the mode, A <sub>0</sub> , A <sub>2</sub> and A <sub>II</sub> are asserted high (V <sub>IH</sub> ) and A <sub>1</sub> , A <sub>10</sub> and A <sub>12</sub> are asserted low (V <sub>IL</sub> ), allow 5 µsec for circuit recovery time before returning the device for normal operation. |

| Input | Output     |  |

|-------|------------|--|

| MR    | DQ0, DQ16  |  |

| RAS   | DQ1, DQ17  |  |

| CAS   | DQ2        |  |

| DQM   | DQ18       |  |

| CS    | DQ3        |  |

| WORD  | DQ19       |  |

| A12   | DQ4        |  |

| A11   | DQ20       |  |

| A10   | DQ5        |  |

| A0    | DQ21       |  |

| A1    | DQ6, DQ22  |  |

| A2    | DQ7, DQ23  |  |

| A3    | DQ8, DQ24  |  |

| A4    | DQ9, DQ25  |  |

| A5    | DQ10       |  |

| A6    | DQ26       |  |

| A7    | DQ11       |  |

| A8    | DQ27       |  |

| A9    | DQ12       |  |

| CKE   | DQ28       |  |

| CLK   | DQ13, DQ29 |  |

| WE    | DQ14, DQ30 |  |

| VPP   | DQ15, DQ31 |  |

### **Input - Output Pin Pairs**

### Asynchronous Boot Block

The AT49LD3200B will automatically activate the Asynchronous Boot Block after power-up and the AT49LD3200 can activate the Asynchronous Boot Block through the Mode Register Set. The size of the boot block is 8K x 16 bits with addresses  $A_0 \sim A_{12}$  and outputs  $DQ_0 \sim DQ_{15}$ . The contents of the boot block are accessed asynchronously, meaning the data at outputs will change according to the address inputs after  $t_{ACC}$ , without any external clocking signals.

Programs and erases are performed using the synchronous bus cycle operation (refer to Command Definitions table and Program Cycle and Erase Cycle waveforms) after the boot block is activated either through power-up or Mode Register Set. Programming of the boot block is set up for x16 mode.

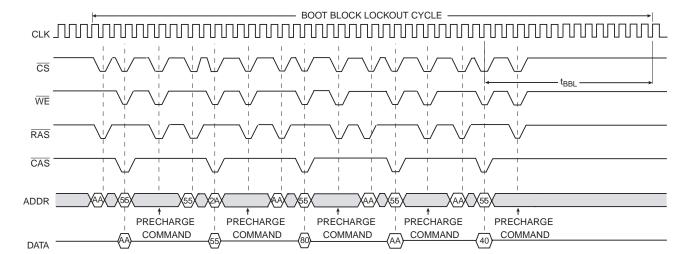

This Asynchronous Boot Block has a lockout feature that prevents programming or erasing of data in this boot block once the feature has been enabled. This feature does not have to be activated; the boot block's usage as a protected region is optional to the user. Once this feature is enabled, the data in the boot block can no longer be erased or programmed when input levels of 3.6V or less are used. To activate the lockout feature,

Boot Block Lockout command, which is a synchronous five-bus cycle operation, must be performed (refer to Command Definitions table and Program Cycle Waveforms).

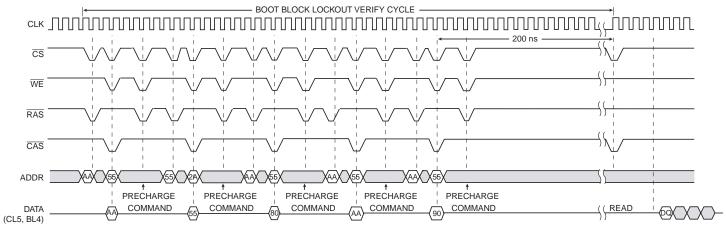

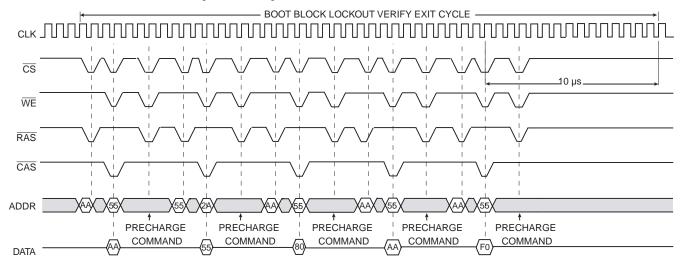

A software method is available to determine if programming or erasing of the boot block is locked out. Issue Boot Block Lockout Verify command and observe  $DQ_0 \sim DQ_7$ . If the data show 00H/02H, the boot block can be programmed or erased; if the data show 01H/03H, the lockout feature has been enabled and the boot block cannot be programmed or erased. The Boot Block Lockout Verify Exit command should be used to return to standard operation (refer to Command Definition table and Boot Block Lockout Verify Waveforms).

The user can override the boot block lockout by taking the  $\overline{\text{MR}}$  pin to 12 volts after the boot block is activated. When the  $\overline{\text{MR}}$  pin is brought back to TTL levels, the boot block lockout feature is again active.

# Command Definition in Hex<sup>(1)</sup>

| Command                              | Bus    | 1st | Bus C | ycle | 2nd | Bus C | ycle | 3rd | Bus C | ycle | 4th | Bus C | ycle            | 5th | Bus C | ycle | 6th               | Bus C | ycle |

|--------------------------------------|--------|-----|-------|------|-----|-------|------|-----|-------|------|-----|-------|-----------------|-----|-------|------|-------------------|-------|------|

| Sequence                             | Cycles | RA  | CA    | Data            | RA  | CA    | Data | RA                | CA    | Data |

| Word/<br>Double<br>Word<br>Program   | 4      | AA  | 55    | AA   | 55  | 2A    | 55   | AA  | 55    | A0   | RA  | CA    | D <sub>IN</sub> |     |       |      |                   |       |      |

| Sector<br>Erase                      | 6      | AA  | 55    | AA   | 55  | 2A    | 55   | AA  | 55    | 80   | AA  | 55    | AA              | 55  | 2A    | 55   | SA <sup>(2)</sup> | х     | 30   |

| Continuity<br>Test Mode<br>Entry     | 5      | AA  | 55    | AA   | 55  | 2A    | 55   | AA  | 55    | 80   | AA  | 55    | AA              | AA  | 55    | 70   |                   |       |      |

| Boot Block<br>Lockout                | 5      | AA  | 55    | AA   | 55  | 2A    | 55   | AA  | 55    | 80   | AA  | 55    | AA              | AA  | 55    | 40   |                   |       |      |

| Boot Block<br>Lockout<br>Verify      | 5      | AA  | 55    | AA   | 55  | 2A    | 55   | AA  | 55    | 80   | AA  | 55    | AA              | AA  | 55    | 90   |                   |       |      |

| Boot Block<br>Lockout<br>Verify Exit | 5      | AA  | 55    | AA   | 55  | 2A    | 55   | AA  | 55    | 80   | AA  | 55    | AA              | AA  | 55    | F0   |                   |       |      |

Notes: 1. The DATA FORMAT in each bus cycle is as follows: DQ31 - DQ8 (Don't Care); DQ7 - DQ0 (Hex).

2. SA = Sector Addresses: Any word/double word address within a sector can be used to designate the sector address. See Sector Address Mapping table below.

3. Allow minimum 200 ns after Boot Block Lockout Verify command and before Read.

4. Allow minimum 10 µs after Boot Block Lockout Verify Exit command for the device to return to standard operation.

|        |                         |                   | (16<br>ss Range    | x32<br>Address Range |                    |  |

|--------|-------------------------|-------------------|--------------------|----------------------|--------------------|--|

| Sector | Size (Word/Double Word) | CA <sub>7-0</sub> | RA <sub>12-0</sub> | CA <sub>6-0</sub>    | RA <sub>12-0</sub> |  |

| SA0    | 256K/128K               | x                 | 00XX<br>03XX       | x                    | 00XX<br>03XX       |  |

| SA1    | 256K/128K               | x                 | 04XX<br>07XX       | X                    | 04XX<br>07XX       |  |

| SA2    | 256K/128K               | x                 | 08XX<br>0BXX       | X                    | 08XX<br>0BXX       |  |

| SA3    | 256K/128K               | x                 | 0CXX<br>0FXX       | X                    | 0CXX<br>0FXX       |  |

| SA4    | 256K/128K               | x                 | 10XX<br>13XX       | X                    | 10XX<br>13XX       |  |

| SA5    | 256K/128K               | x                 | 14XX<br>17XX       | X                    | 14XX<br>17XX       |  |

| SA6    | 256K/128K               | x                 | 18XX<br>1BXX       | x                    | 18XX<br>1BXX       |  |

| SA7    | 256K/128K               | Х                 | 1CXX<br>1FXX       | х                    | 1CXX<br>1FXX       |  |

### Sector Address Mapping

# **Basic Feature and Function Descriptions**

### MRS

### **Clock Suspend**

: This command cannot be activated.

### **Clock Suspend Exit and Power-down Exit**

Note: After Mode Register Set command is completed, no new commands can be issued for 3 clock cycles, and MR or CS should be fixed "H" within a minimum of 3 clock cycles.

### **DQM** Operation

Note: DQM makes data out high-Z after 2 CLKs, which should be masked by CKE "L".

Note: When the burst length is 4 at 66 MHz,  $t_{RC}$  is equal to 6 clock cycles.

AT49LD3200(B)

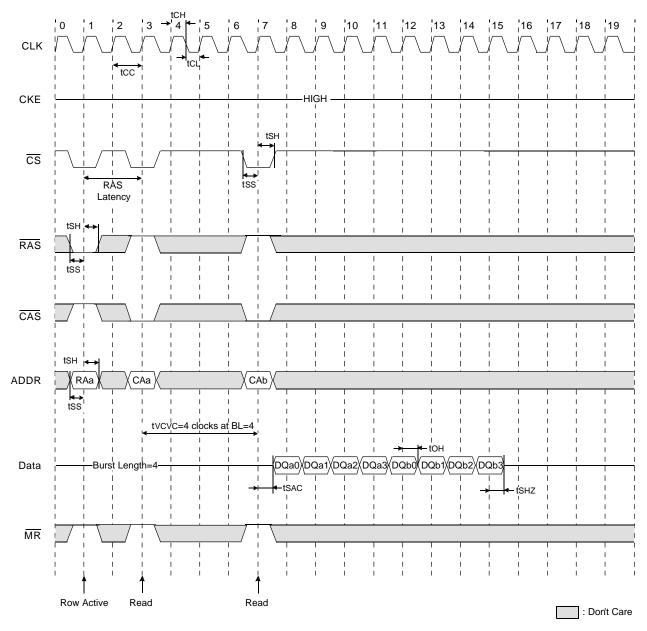

### Read Cycle II: Consecutive Column Access @RAS Latency = 2, CAS Latency = 5, Burst Length = 4

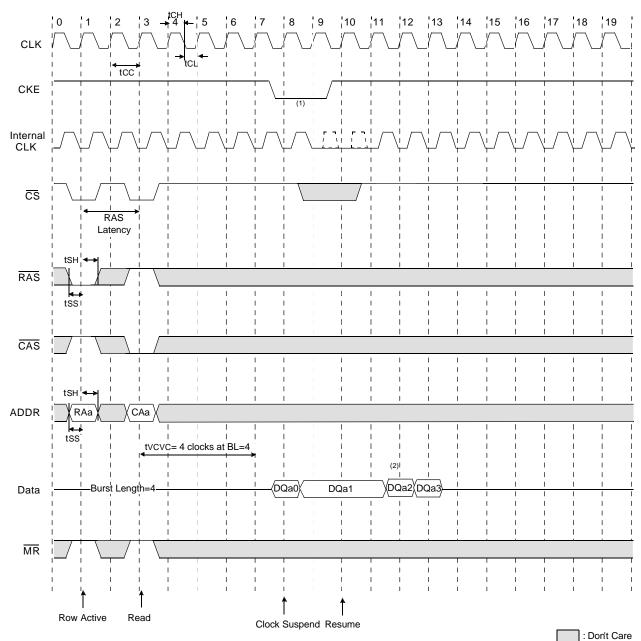

#### Read Cycle III: Clock Suspend @RAS Latency = 2, CAS Latency = 5, Burst Length = 4

AT49LD3200(B)

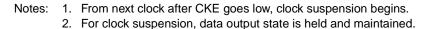

Read Interrupted by Precharge Command and Burst Read Stop Cycle @Burst Length = 8

Notes: 1. The Burst Stop command is valid at every page burst length. The data bus goes to high-Z after the CAS latency from the Burst Stop command is issued.

2. The interval between Read command (column address presented) and Burst Stop command is 1 cycle (min).

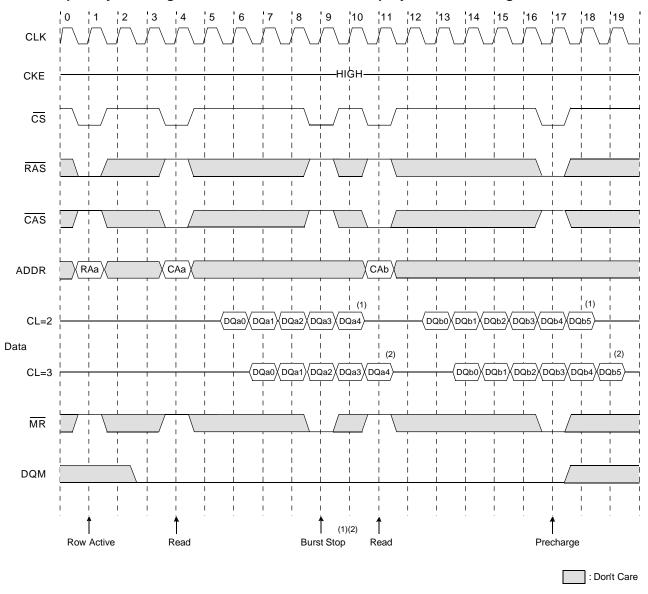

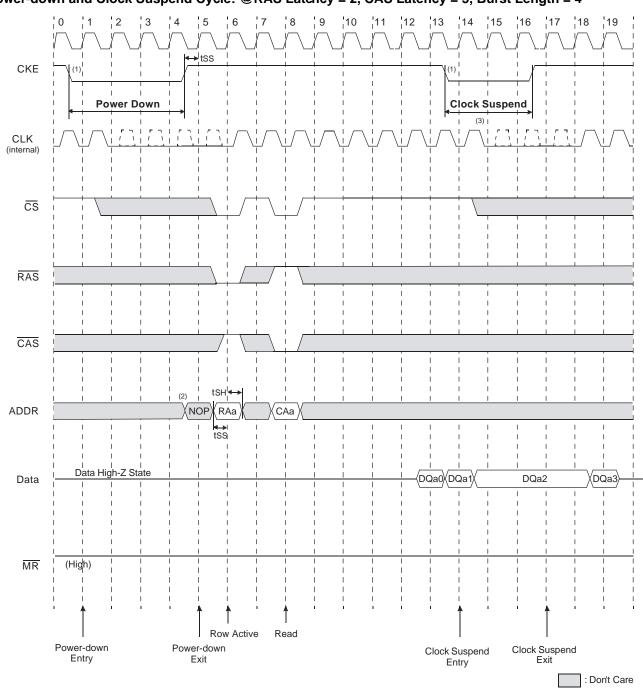

#### Power-down and Clock Suspend Cycle: @RAS Latency = 2, CAS Latency = 5, Burst Length = 4

Notes: 1. From next clock after CKE goes low, clock suspend and power-down begins.

2. After power-down exit, NOP should be issued and new command can be issued after 1 clock.

3. Clock suspend is in active standby mode.

# AT49LD3200(B)

### Mode Register Set: @RAS Latency = 2, CAS Latency = 5, Burst Length = 4

Notes: 1. After the Mode Register Set is completed, no new commands can be issued for 3 CLK cycles.

After power-up, necessarily Mode Register Set should be completed at least one time and CS or MR must be fixed "H" within 3 clock cycles, and when user wants to change Mode Register Set, user must exit from power-down mode and start Mode Register Set before chip enters normal operation mode.

# **Detailed Functional Truth Table**

| Current                          |     |    | Input | Signal |    |      |                                                                                                                                                                                                   |

|----------------------------------|-----|----|-------|--------|----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| State                            | CKE | CS | RAS   | CAS    | MR | Add. | Next State Operation                                                                                                                                                                              |

|                                  | L   | Х  | Х     | Х      | Х  | Х    | Power-down                                                                                                                                                                                        |

| After<br>Power-up <sup>(1)</sup> | Н   | L  | L     | н      | Н  | RA   | Row Active; latch RA                                                                                                                                                                              |

|                                  | Н   | L  | L     | L      | L  | Code | Mode Register Set                                                                                                                                                                                 |

|                                  | н   | L  | L     | н      | Н  | RA   | If consecutive row access is issued within $t_{RC}$ (min.) without CAS enabling, only the final RA is valid.                                                                                      |

| Row Active                       | Н   | L  | Н     | L      | Н  | CA   | Begin READ; latch CA                                                                                                                                                                              |

|                                  | Н   | L  | L     | L      | L  | Code | Illegal <sup>(1)</sup>                                                                                                                                                                            |

|                                  | L   | Х  | Х     | Х      | Х  | Х    | Clock Suspend                                                                                                                                                                                     |

|                                  | Н   | L  | L     | Н      | Н  | RA   | Row Access in Read State, within the $t_{RC}$ , previous read is ignored and new row is activated. Beyond the $t_{RC}$ , previous read is completed and new read begins.                          |

| READ                             | Н   | L  | н     | L      | Н  | CA   | Consecutive Column Access, within the $t_{VCVC}$ , only the final CA is valid and the previous burst read is ignored. Beyond the $t_{VCVC}$ , the previous read is completed and new read begins. |

|                                  | Н   | L  | L     | Н      | L  | Х    | NOP (after Burst Read)/Read Interrupt                                                                                                                                                             |

|                                  | Н   | L  | Н     | н      | L  | Х    | NOP (after Burst Read)/Read Interrupt                                                                                                                                                             |

|                                  | Н   | L  | L     | L      | L  | Code | Illegal <sup>(1)</sup>                                                                                                                                                                            |

|                                  | L   | Х  | Х     | Х      | Х  | Х    | Clock Suspend/Power-down                                                                                                                                                                          |

| Any State                        | L   | L  | L     | L      | Н  | Х    | Low Power Consumption Mode                                                                                                                                                                        |

| Any State                        | Н   | L  | Н     | н      | Н  | Х    | NOP                                                                                                                                                                                               |

| Amy Ctata                        | н   | L  | L     | L      | Н  | Х    | Illegal                                                                                                                                                                                           |

| Any State                        | Н   | L  | Н     | L      | L  | CA   | Illegal                                                                                                                                                                                           |

Note: 1. After the power-up, when user wants to change MR Set, user must exit from power-down mode and start MR Set before chip enters normal operation mode.

## **Technical Notes**

### Frequency vs. AC Parameter Relationship Table<sup>(1)</sup>

### <u><</u>100 MHz

| Burst Length | RAS Latency | CAS Latency t <sub>RC</sub> (min) |    | t <sub>vcvc</sub> (min) |

|--------------|-------------|-----------------------------------|----|-------------------------|

|              | 2           | 6                                 | 7  | 5 <sup>(2)</sup>        |

| 4            | 2           | 7                                 | 8  | 6                       |

| 0            | 2           | 6                                 | 11 | 9 <sup>(2)</sup>        |

| 8            |             | 7                                 | 12 | 10                      |

### <u><</u>75 MHz

| Burst Length | RAS Latency | CAS Latency t <sub>RC</sub> (min) t |    | t <sub>vcvc</sub> (min) |

|--------------|-------------|-------------------------------------|----|-------------------------|

| 4            | 2           | 5                                   | 6  | 4 <sup>(2)</sup>        |

| 4            | 2           | 6                                   | 7  | 5                       |

| 0            | 2           | 5                                   | 10 | 8 <sup>(2)</sup>        |

| 8            |             | 6                                   | 11 | 9                       |

#### <u><</u>50 MHz

| Burst Length | RAS Latency | CAS Latency | t <sub>RC</sub> (min) | t <sub>vcvc</sub> (min) |

|--------------|-------------|-------------|-----------------------|-------------------------|

|              |             | 4           | 4 <sup>(2)</sup>      | 3/4 <sup>(2)</sup>      |

| 4            | 1           | 5           | 5                     | 4 <sup>(2)</sup>        |

|              |             | 6           | 6                     | 5                       |

|              |             | 4           | 8 <sup>(2)</sup>      | 7/8 <sup>(2)</sup>      |

| 8            | 1           | 5           | 9                     | 8(2)                    |

|              |             | 6           | 10                    | 9                       |

Notes: 1. Above tables are not specifications values, but rather the actual number of clock cycles. There are no gapless operations for CAS latency 7 and 8.

2. Minimum clocks for gapless operation.

t<sub>RC</sub> (max) = t<sub>VCVC</sub> (max) = 50 μs. If t<sub>RC</sub> (max) or t<sub>VCVC</sub> (max) has been reached, a new "ACTIVE" command is necessary for new access.

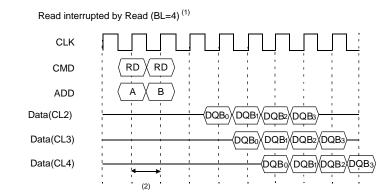

### **CAS** Interrupt

- Notes: 1. By "Interrupt", it is meant to stop Burst Read by external command before the end of burst. By "CAS Interrupt", to stop Burst Read by CAS access.

- 2. CAS to CAS delay (=1 CLK).

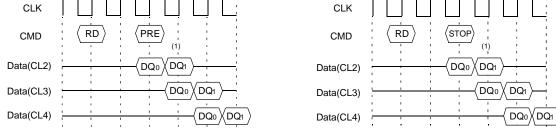

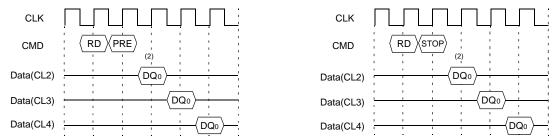

### Read Interrupt Operation by Issuing the Precharge of Burst Stop Command

CASE I ) Issued read Interrupt command during burst read operation period.

CASE II ) Issued read Interrupt command between read command and data out.

Notes: 1. The data bus goes to high-Z after CAS latency from the Burst Stop (or precharge) command.

2. Valid output data will last up to CL-1 clock cycle from PRE command.

### Read Cycle Depending on t<sub>RC</sub>

### @RL = 2, CL = 6, BL = 4; 100 MHz

#### @RL = 2, CL = 5, BL = 4; 75 MHz

#### @RL = 1, CL = 4, BL = 4; 50 MHz

### Read Cycle Depending on $t_{VCVC}$

### @RL = 2, CL = 6, BL = 4; 100 MHz

#### @RL = 2, CL = 5, BL = 4; 75 MHz

#### @RL = 1, CL = 4, BL = 4; 50 MHz

# AC Characteristics for Boot Block Read Operation

| Symbol           | Parameter                | Condition                                     | Min | Max | Units |

|------------------|--------------------------|-----------------------------------------------|-----|-----|-------|

| t <sub>ACC</sub> | Address to Output Delay  | CS = DQM<br>= V <sub>IL</sub>                 |     | 170 | ns    |

| t <sub>OE</sub>  | DQM to Output Delay      | $\overline{\text{CS}} = \text{V}_{\text{IL}}$ |     | 60  | ns    |