CPLD eksplike: yon gid pou aparèy lojik pwogramasyon

Nan mond lan dinamik nan konsepsyon elektwonik, konplèks aparèy lojik pwogramasyon (CPLDs) kanpe deyò kòm zouti versatile, transparans melanje adaptabilite, presizyon, ak efikasite.Aparèy sa yo revolusyone konsepsyon sikwi pa entwodwi pwogramasyon selil macro ak yon matris dominan konekte, pèmèt kreyasyon an nan fonksyon lojik konplike ak remakab fyab.Soti nan kòmansman yo nan ane 1980 yo nan wòl kle yo nan endistri modèn tankou rezo, otomobil, ak avyon, CPLDs te pwouve voulu pou ou ap chèche tou de fleksibilite ak pèfòmans.Atik sa a fouye nan vwayaj la nan CPLDs, karakteristik diferan yo, aplikasyon pou pratik, ak metodoloji yo pwogramasyon ki fè yo yon poto nan konsepsyon lojik dijital.Katalòg

Apèsi sou lekòl la nan CPLD

Nan dominasyon an nan aparèy lojik konplèks pwogramasyon (CPLDs), yon sèl dekouvri yon Tapestry sofistike nan pwogramasyon lojik pwogramasyon macro, mele nan yon matris entè -konekte dominan.Sa yo selil macro (MC) ak opinyon/pwodiksyon (I/O) liy inite pèmèt ou adrwatman konsepsyon sikwi, konfigirasyon estrikti yo pou fonksyon inik.Kontrèman ak aparèy ki anbarase pa distribisyon konplèks yo konekte, CPLDs itilize fil metal immobilier.Karakteristik sa a bay sou yo yon konpòtman revèy ki konsistan ak prévisible, fè prediksyon distribisyon plis serye ak egzak.

Vwayaj la ak itilizasyon

Ane 1970 anonse avènement de aparèy lojik pwogramasyon (PLDs), ankouraje yon mouvman nan direksyon pou inite macro pwogramasyon.Chanjman sa a prezante ase fleksibilite konsepsyon, mete yo apa de sikwi estatik dijital, byenke yo te sèvis piblik yo okòmansman contrainte sikwi ki pi senp.Avènement de CPLDs nan mitan ane 1980 yo revolusyone jaden flè sa a, pavaj yon fason pou desen sikwi konplèks.Depi lè sa a, yo te tise tèt yo nan twal la nan endistri tankou rezo, otomobil elektwonik, CNC D ', ak sistèm avyon.Ou ka reminisce sou fason CPLDs pwosesis senplifye ki yon fwa mande metikuleuz travay manyèl, regilye nèf semenn klas yon kwasans remakab nan efikasite.

Kalite diferan nan cplds

CPLDs yo fè distenksyon ant tèt yo nan pwogram adaptab yo, entegrasyon vaste, kapasite devlopman rapid, ak aplikasyon lajè, ansanm ak depans pwodiksyon ékonomi.Yo fè apèl a moun ki gen eksperyans pyès ki nan konpitè minim, sèvi kòm pwodwi serye ak sekirite ki pa nesesè pou fè tès konplè.Kòm yon testaman nan gwo abilite yo nan gwo-echèl desen sikwi, CPLDs jwe yon wòl kle nan devlopman pwototip ak sèvi kouri anba a 10,000 inite, enkòpore yon konpetans itil pou ou.Adeptite a ak ki CPLDs ajiste nan en demand pwojè souvan touche yo apresyasyon, mete aksan sou adaptabilite aktyèl yo nan anviwònman dinamik.

Metòd aplikasyon

Sa yo sikwi entegre pèmèt ou elabore sou fonksyon lojik pwepare a bezwen yo lè l sèvi avèk tou de chema ak pyès ki nan konpitè deskripsyon lang sou tribin devlopman.Pou egzanp, nan konsepsyon yon machin reponn, chema, ak deskripsyon pyès ki nan konpitè yo prepare ak konpile sou yon òdinatè.Itilize yon kab download, se kòd la transfere nan CPLD a pou nan-sistèm pwogramasyon, ki konprann tès, depanaj, ak desen amelyore.Desen avèk siksè fabrike yo Lè sa a, mas-pwodwi pa repwodui bato CPLD.Nan pwojè tankou sistèm limyè trafik, repete pwosesis la konsepsyon vin nesesè, menm jan ak rebati yon kay retabli nouvote li yo.Metodoloji repetitif sa a souvan mete baz pou metrize, pou ranfòse tou de ladrès ak konfyans.

Dirijan varyant

Pandan tout ane yo, konpayi tankou Altera, lasi, ak Xilinx te revele liy enpòtan nan CPLDs.Egzanp enpòtan pou remake gen ladan Altera a EPM7128S, Lasi a LC4128V, ak xilinx la XC95108 .Modèl sa yo te jwenn wòl enpòtan atravè divès aplikasyon mondyal.Moun ki te gen privilèj pou yo travay avèk pwodwi distenk sa yo souvan remake sou diferans ki sibtil ankò pwisan ki optimize fonksyonalite patikilye.Sa a reflete yon pwosesis seleksyon amann enfliyanse pa demand pwojè espesifik, kote chak Variant kenbe apèl inik li yo.

Idantifikasyon ak klasifikasyon nan FPGA ak CPLD

|

Aspè |

CPLD |

FPGA |

|

Fòmasyon konpòtman lojik |

Fòm konpòtman lojik lè l sèvi avèk estrikti tèm pwodwi.

Egzanp: seri ISPLSI lasi, Xilinx XC9500 Seri, Altera Max7000s

Seri, Seri Lattice Mach |

Fòm konpòtman lojik lè l sèvi avèk yon metòd Passage tab.

Egzanp: Xilinx Seri Spartan, Altera Flex10K, Acex1k Seri |

|

Konvisib |

Apwopriye pou algoritm ak lojik konbinezon, travay

Pi bon ak deklanchman limite ak tèm pwodwi ki rich |

Apwopriye pou lojik sekans, travay pi byen ak

Estrikti ki rich nan deklanchman |

|

Distribisyon reta |

Estrikti fil elektrik kontinyèl bay inifòm ak

reta distribisyon previzib |

Estrikti fil elektrik segmenté mennen nan distribisyon enprevizib

reta |

|

Pwogramasyon fleksibilite |

Sikwi entèn fiks yo modifye pou pwogramasyon an.

Lojik blòk-nivo pwogramasyon yo itilize |

Se fil elektrik entèn modifye pou pwogramasyon.Lojik

Gate-nivo pwogramasyon pèmèt pi gwo fleksibilite |

|

Entegrasyon |

Pi ba entegrasyon konpare ak FPGA |

Pi wo entegrasyon ak estrikti fil elektrik pi konplèks ak

Aplikasyon lojik |

|

Fasilite nan itilize |

Pi fasil pou itilize ak pwogramasyon via E2PROM oswa FastFlash.

Pa gen okenn chip memwa ekstèn obligatwa |

Mande pou memwa ekstèn nan magazen pwogramasyon

enfòmasyon, ki mennen ale nan l 'pi konplèks |

|

Vitès ak previzibilite |

Pi vit vitès ak pi bon previzibilite distribisyon akòz

Lumped interconnexion ant blòk lojik |

Pi dousman vitès ak mwens previzib distribisyon akòz

Gate-nivo pwogramasyon ak distribye interconnexion |

|

Teknoloji pwogramasyon |

Sèvi ak pwogram E2PROM oswa Flash memwa.Done pwogramasyon

se kenbe lè se sistèm nan mache koupe.Sipòte pwogramasyon sou yon

pwogramè oswa nan-sistèm |

Ki baze sou pwogram SRAM.Done pwogramasyon pèdi lè

Sistèm lan mache epi yo dwe rechargé.Sipòte dinamik

konfigirasyon |

|

Konfidansyalite |

Ofri pi bon konfidansyalite |

Bay pi ba konfidansyalite |

|

Konsomasyon pouvwa |

Jeneralman pi wo konsomasyon pouvwa, espesyalman ak

Pi wo entegrasyon |

Pi ba konsomasyon pouvwa konpare ak CPLD |

Pwogramasyon lang CPLD

Analize ki jan konplèks aparèy lojik pwogramasyon (CPLDs) yo pwograme se yon poto nan élaboration solisyon pyès ki nan konpitè versatile.Metòd istorik yo pou pwogramasyon CPLDS te konte sou dyagram nechèl oswa pyès ki nan konpitè deskripsyon lang (HDLs), ak Verilog HDL ak VHDL yo te chwa dominant.Lang la chwazi ka fòme tou de estrateji nan konsepsyon ak efikasite nan operasyonèl nan en.

• Verilog HDL: Verilog HDL se pran swen pou sentaks senp li yo ak kapasite simulation gaya, reflete metodoloji yo itilize nan konsepsyon lojik dijital.Entegrasyon li yo ak zouti elektwonik konsepsyon automatisation (EDA) pèmèt ou transparans fè sentèz ak simulation.Te sentaks la C-tankou nan Verilog obsève pi ba baryè a nan antre pou moun ki gen orijin pwogramasyon, prese vwayaj la soti nan konsepsyon deplwaman atravè yon gwo ranje nan sektè endistriyèl.

• VHDL: VHDL bay yon opsyon plis elabore ak espresif pou pwogramasyon HDL.Li se souvan chwa a pou pwojè ki mande dokiman metikuleu ak rijid kalite-tcheke, karakteristik ki vo nan endistri yo avyon ak defans.Ou ka sonje ke malgre konpleksite potansyèl VHDL a nan pi piti pwojè, estrikti disipline li yo sipòte kreyasyon an nan desen eksepsyonèlman serye, yon nesesite nan anviwònman kote sekirite se dominan.

Sou nou

ALLELCO LIMITED

Li piplis

Quick Inquiry

Tanpri voye yon ankèt, nou pral reponn imedyatman.

NMOS tranzistò: konsepsyon, operasyon, ak aplikasyon pou

sou 2024/12/29

Vit Fourier transfòme an (FFT): revolusyone pwosesis siyal dijital

sou 2024/12/29

Posts popilè

-

Enstriksyon konplèks Set Odinatè: Ki jan yo chanje informatique?

sou 8000/04/18 147764

-

USB-C pinout ak karakteristik

sou 2000/04/18 111987

-

Sèvi ak Xilinx Inifye Simulation Primitif: Yon Gid konplè nan FPGA Design ak Simulation

sou 1600/04/18 111351

-

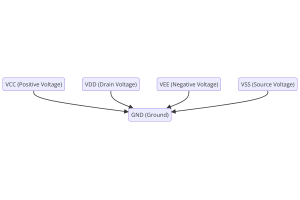

Tansyon ekipman pou pouvwa nan elektwonik: siyifikasyon VCC, VDD, VEE, VSS, ak GND

sou 0400/04/18 83751

-

RJ45 Connector Gid: Pinout, fil elektrik, Kalite Kab, ak Itilizasyon

sou 1970/01/1 79544

-

Gid la ultim nan kòd koulè fil nan sistèm elektrik modèn

Fason sistèm elektrik nou yo itilize koulè yo pa sèlman pou sanble.Chak koulè fil kounye a endike yon fonksyon espesifik, fè li pi fasil yo idantifye ak okipe konpozan elektrik kòrèkteman pandan en...sou 1970/01/1 66949

-

Purge Valv Gid: Fonksyon, sentòm, tès, ak ranplasman pou pèfòmans motè optimal

Valv la weteur se yon pati enpòtan nan sistèm yon machin nan ki ede kenbe lè a pwòp pa jere vapè gaz yo anvan yo ka chape anba nan atmosfè a.Sa a pa sèlman ede anviwònman an pa diminye polisyon, me...sou 1970/01/1 63092

-

Kalite (q) Faktè: Ekwasyon ak aplikasyon

Faktè bon jan kalite a, oswa 'Q', se enpòtan lè tcheke ki jan byen endukteur ak rezonan travay nan sistèm elektwonik ki itilize frekans radyo (RF).'Q' mezire ki jan byen yon sikwi minimize pèt enèj...sou 1970/01/1 63028

-

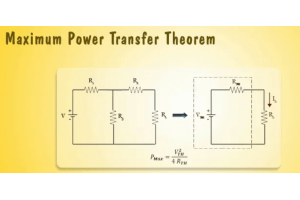

Atenn pèfòmans pik ak teyorèm nan transfè pouvwa maksimòm

Teyorèm maksimòm transfè pouvwa a eksplike kijan enèji ki sòti nan yon sous, tankou yon batri oswa dèlko, ap koule nan yon chaj ki konekte.Li montre kondisyon an egzak kote chaj la resevwa pouvwa k...sou 1970/01/1 54092

-

Espesifikasyon batri A23 ak konpatibilite

Batri a A23 se yon ti, silenn ki gen fòm batri ak vòltaj segondè.Yo te rele tou 23a, 23AE, oswa MN21, li kouri nan 12 vòlt ak pi wo pase AA oswa AAA pil.Konsepsyon espesyal li fè li pafè p...sou 1970/01/1 52172