Comprehensive Gid pou Testbenches: Zouti ak teknik pou verifikasyon sistèm dijital

Gid sa a eksplore TestBenches, yon zouti kle pou validasyon lojisyèl ki simulation kondisyon yo teste entrain ak verifye rezilta yo.Testbenches jwe yon wòl nan idantifye pinèz byen bonè nan devlopman, amelyore fyab lojisyèl.Avèk egzanp pratik ak Sur, atik sa a mete aksan sou itilizasyon yo, teknik, ak enpòtans nan bati fò, efikas sistèm dijital.Katalòg

Wòl nan testbenches nan validasyon sistèm dijital

Yon testbench se yon eleman nan pwosesis la nan validasyon sistèm dijital.Li se pa senpleman yon zouti pou génération entrain ak verifye rezilta, li sèvi kòm yon fondasyon konplè ki simulation kondisyon yo evalye fyab la, fonctionnalités, ak konpòtman nan sistèm dijital yo anvan yo yo deplwaye nan jaden an.Pa kreye anviwònman kontwole nan sistèm estrès-tès ak nan yon pakèt domèn senaryo opinyon, TestBenches ede ou idantifye defo potansyèl konsepsyon byen bonè nan lifecycle nan devlopman, lontan anvan yo mete sistèm lan nan pwodiksyon.Deteksyon sa a byen bonè nan pinèz ak frajilite ki nesesè pou diminye erè koute chè, asire konfòmite ak espesifikasyon pèfòmans, ak amelyore fyab sistèm jeneral.

Anplis de verifye Correct nan repons sistèm lan, testbenches jwe yon wòl nan evalye ka kwen, pwoblèm distribisyon, ak mekanis erè-manyen, asire sistèm lan ka opere kòrèkteman menm anba kondisyon ekstrèm oswa inatandi.Atravè tès otomatik ak simulation, testbenches kontribye nan pi wo bon jan kalite lojisyèl, pèfòmans amelyore, ak pi kout sik devlopman pa pèmèt tès repete san yo pa entèvansyon manyèl.Yo sèvi kòm yon pwoteksyon kont echèk ki ta ka rive apre deplwaman, asire fyabilite a ak disponiblite nan sistèm dijital.

Eleman kle nan yon testbench ak fonksyon yo

Pi byen konprann ki jan Testbenches opere, li enpòtan yo eksplore eleman yo ki fè yo efikas.Yon Testbench ki byen fabrike opere pa jere de travay debaz: génération entrain (stimuli) ak verifye rezilta yo.Ann egzaminen chak eleman an detay.

Jenerasyon estimilis

Jenerasyon estimilis enplike nan kreye yon seri siyal opinyon ki simulation kondisyon yo teste konpòtman an nan yon sistèm dijital.Sa yo entrain bezwen tou de egzak ak reyalis asire se sistèm lan sibi yon varyete de senaryo li ta ka rankontre nan pratik.Konsidere yon modil RAM debaz kòm yon egzanp.Testbench a dwe bay entrain espesifik nan modil la epi obsève rezilta li yo asire li konpòte li jan yo espere a.Entran yo kle pou yon modil RAM tipikman gen ladan yo:

• CLK (revèy): kondwi tan an nan sistèm lan.

• Addr (adrès): Espesifye ki kote done yo jwenn aksè.

• WEN (ekri pèmèt): kontwole si done yo ekri nan memwa.

• Done: enfòmasyon aktyèl la ke yo te ekri nan modil la.

Pwodiksyon an, yo konnen kòm Dataout, reprezante rezilta a nan operasyon entèn modil la.Pa ak anpil atansyon scripting ki jan sa yo entrain yo lage ak siveyans doneout, ou ka verifye ke sistèm lan fè kòrèkteman anba senaryo diferan.Panse a jenerasyon estimilis kòm mete kanpe yon senaryo tès nan yon laboratwa.Menm jan syantis yo ak anpil atansyon kontwole kondisyon yo obsève reyaksyon chimik, konsèpteur dijital navèt entrain egzak yo obsève ki jan yon sistèm reponn.

Verifikasyon pwodiksyon

Verifikasyon pwodiksyon se pwosesis la nan tcheke ke rezilta aktyèl sistèm lan matche ak rezilta yo espere.Etap sa a se kritik nan pwan erè bonè anvan yo evolye nan pi gwo pwoblèm.Lòt moun sèvi ak verifikasyon pwodiksyon konfime ke sistèm lan satisfè fonksyonalite gen entansyon li yo ak fè toujou nan kondisyon divès kalite.Verifikasyon pwodiksyon enplike nan tou de otomatik ak chèk manyèl.Pou egzanp:

• Zouti verifikasyon otomatik: zouti tankou Modelsim ak Quartus pèmèt pou tès otomatik, kote rezilta yo sistèm yo konpare ak rezilta espere.Sa a vitès moute pwosesis la verifikasyon ak diminye erè.

• Verifikasyon Manyèl (si ou vle): Pou senaryo pi konplèks, chèk manyèl ka nesesè pou asire ke ka kwen espesifik yo kouvri.

Zouti ak teknik pou aplikasyon testbench

Quartus: vizyèl opinyon/pwodiksyon simulation

Quartus bay yon koòdone grafik ki vizyèlman fè aranjman pou entrain ak obsève rezilta yo.Metòd sa a ka benefisye pou débutan oswa pou sistèm ki mande pou yon plis men-sou, apwòch vizyèl.Pa pèmèt yo kominike avèk yon simulation nan yon anviwònman grafik, Quartus ede demistifye relasyon ki genyen ant entrain ak rezilta, fè li pi fasil yo konprann ki jan yon sistèm dijital konpòte li nan tan.Youn nan fòs kle yo nan Quartus se ke li se ideyal pou débutan.Entwisyon li yo, koòdone vizyèl bay yon fason ki dwat yo wè ki jan entrain afekte rezilta san yo pa bezwen an pou scripting vaste oswa konesans pwogramasyon.Fidbak la li ofri ede atrab konpòtman an nan sikwi pi fasil, fè li yon zouti itil pou moun ki nouvo nan konsepsyon sistèm dijital.Sepandan, Quartus gen limit li yo.Mete kanpe similasyon nan Quartus ka tan konsome, patikilyèman pou desen pi konplèks.Zouti a se mwens fleksib konpare ak scripting ki baze sou zouti simulation, ki ka ofri plis personnalisation ak opsyon automatisation.Pou travay sou gwo-echèl oswa sistèm trè detaye, sa a mank de fleksibilite ka poze yon defi.

Modelsim: tèks ki baze sou simulation lè l sèvi avèk scripting

Modelsim pran yon apwòch diferan nan simulation pa priyorite tèks ki baze sou opinyon nan scripting.Kreye senaryo tès lè l sèvi avèk Verilog (.v) oswa VHDL (.vhd) Scripts, olye ke vizyèlman fè aranjman pou fè entrain ak rezilta.Metòd sa a bay plis presizyon ak kontwòl.Olye pou yo repoze sou yon koòdone grafik, ou defini kijan sistèm lan ta dwe teste nan Scripts detaye, sa ki pèmèt pou pi gwo personnalisation ak automatisation nan pwosesis la simulation.Youn nan fòs kle Modelsim a se fleksibilite a li ofri.Lè l sèvi avèk Scripts, ou gen plis kontwòl sou senaryo tès, pèmèt yo kreye similasyon konplèks ak egzak.Yon fwa yon designer ki abitye avèk sentaks la ak workflow, mete kanpe similasyon ka pi vit konpare ak lè l sèvi avèk zouti grafik tankou Quartus.Kapasite nan reutilize ak modifye Scripts tou ajoute nan efikasite li yo, patikilyèman nan pi gwo pwojè.Sepandan, apwòch la tèks ki baze sou nan Modelsim vini ak sèten limit.Li mande pou yon konpreyansyon solid nan Verilog oswa sentaks VHDL, ki ka poze yon defi pou débutan ki pa abitye avèk lang deskripsyon pyès ki nan konpitè.Kòm yon rezilta, Modelsim gen yon koub aprantisaj pi apik konpare ak plis zouti simulation vizyèl.Nouvo itilizatè yo ka jwenn li difisil pou kòmanse, men ak pratik, presizyon ak fleksibilite yo ofri nan scripting ka vin yon avantaj ki gen anpil valè.

Ton teyori ak pratik nan verifikasyon

Testbenches sèvi kòm yon pon ant desen teyorik ak aplikasyon pou pa similye ki jan yon sistèm dijital ap konpòte yo anba kondisyon divès kalite, ki gen ladan ka kwen ak entrain inatandi.Nan konsepsyon dijital, li se souvan difisil predi ki jan yon sistèm pral fè nan pratik ki baze sèlman sou modèl teyorik.Testbenches fèmen diferans sa a pa pèmèt ou deplase pi lwen pase konsèp konsepsyon abstrè ak evalye konpòtman yon sistèm nan yon kontwole, anviwònman fo.Youn nan avantaj kle yo nan lè l sèvi avèk zouti simulation nan testbenches se fidbak la enstantane yo bay pandan debogaj.Zouti tankou multisim oswa modèl ofri reprezantasyon vizyèl nan konpòtman sistèm, ki montre ki jan chanjman ki fèt nan entrain enpak rezilta sou tan.Sa a fidbak pèmèt ou identifier pwoblèm pi vit, tras erè tounen nan kòz rasin yo, epi ajiste desen yo kòmsadwa.Pou egzanp, si yon sistèm echwe nan satisfè kontrent distribisyon oswa ekspozisyon konpòtman inatandi anba sèten sekans opinyon, yon testbench ka mete aksan sou sa yo defo imedyatman, lontan anvan se sistèm nan fizikman bati.Pa idantifye pwoblèm byen bonè nan sik la konsepsyon, testbenches diminye bezwen an pou rivork koute chè ak prototip fizik, senplifye pwosesis la verifikasyon.Validasyon sa a byen bonè-etap ede asire ke sistèm dijital yo tou de se fonksyonèl kòrèk ak fleksib nan kondisyon yo, ki fè yo plis serye ak diminye risk pou yo echèk apre deplwaman.Nan fason sa a, Testbenches aji kòm yon zouti pratik pou transfòme desen teyorik nan gaya.

Achitèk avanse testbench

Avanse testbenches ale pi lwen pase senp tès opinyon-pwodiksyon pa enkòpore eleman adisyonèl nan jere sistèm konplèks.Yon testbench estanda gen ladan twa pati kle: a Stimulus dèlko Pou kreye siyal opinyon, yon Design anba tès (DUT), ki se pyès ki nan konpitè aktyèl la ke yo te teste, ak yon Sòti kontwole ki tcheke rezilta yo kont rezilta espere.Konpozan sa yo travay ansanm pou asire verifikasyon plis bon jan ak egzat nan desen dijital.

Amelyore presizyon testbench enplike nan lè l sèvi avèk teknik ki asire yon konsepsyon fè fiable nan senaryo diferan. Tès owaza Entwodwi modèl opinyon enprevizib pou verifye estabilite sistèm lan nan divès kondisyon yo. Tès ka kwen Konsantre sou sitiyasyon fwontyè kote sistèm lan gen plis chans rankontre erè.Anfen, Tès retou annaryè enplike nan re-kouri tès apre chanjman nan konfime ke pa gen okenn nouvo pwoblèm yo te prezante, asire sistèm lan rete ki konsistan ak erè-gratis sou tan.

Scripting testbenches

Pou kreye testbenches efikas ak serye nan Verilog oswa VHDL, swiv kle pi bon pratik.Kòmanse senp, Lè sa a, elaji pa tès fonksyonalite debaz premye ak piti piti ajoute senaryo pi konplèks.Sèvi ak kòmantè ak dokiman pou fè Scripts ou pi fasil pou konprann epi kenbe pa eksplike klèman chak seksyon.Anfen, otomatize kote sa posib pou konsève pou tan ak diminye erè lè l sèvi avèk pasan ak fonksyon okipe travay repetitif ak modèl opinyon.

Sou nou

ALLELCO LIMITED

Li piplis

Quick Inquiry

Tanpri voye yon ankèt, nou pral reponn imedyatman.

Digital faz-fèmen bouk (DPLL): konsepsyon, konpozan, ak operasyon yo

sou 2025/01/7

Evolisyon an ak enpak nan achitekti RISC nan Computing modèn

sou 2025/01/7

Posts popilè

-

Enstriksyon konplèks Set Odinatè: Ki jan yo chanje informatique?

sou 8000/04/18 147778

-

USB-C pinout ak karakteristik

sou 2000/04/18 112033

-

Sèvi ak Xilinx Inifye Simulation Primitif: Yon Gid konplè nan FPGA Design ak Simulation

sou 1600/04/18 111352

-

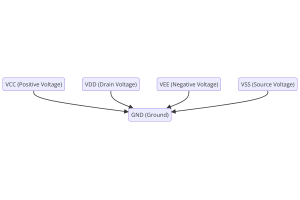

Tansyon ekipman pou pouvwa nan elektwonik: siyifikasyon VCC, VDD, VEE, VSS, ak GND

sou 0400/04/18 83792

-

RJ45 Connector Gid: Pinout, fil elektrik, Kalite Kab, ak Itilizasyon

sou 1970/01/1 79596

-

Gid la ultim nan kòd koulè fil nan sistèm elektrik modèn

Fason sistèm elektrik nou yo itilize koulè yo pa sèlman pou sanble.Chak koulè fil kounye a endike yon fonksyon espesifik, fè li pi fasil yo idantifye ak okipe konpozan elektrik kòrèkteman pandan en...sou 1970/01/1 66976

-

Purge Valv Gid: Fonksyon, sentòm, tès, ak ranplasman pou pèfòmans motè optimal

Valv la weteur se yon pati enpòtan nan sistèm yon machin nan ki ede kenbe lè a pwòp pa jere vapè gaz yo anvan yo ka chape anba nan atmosfè a.Sa a pa sèlman ede anviwònman an pa diminye polisyon, me...sou 1970/01/1 63110

-

Kalite (q) Faktè: Ekwasyon ak aplikasyon

Faktè bon jan kalite a, oswa 'Q', se enpòtan lè tcheke ki jan byen endukteur ak rezonan travay nan sistèm elektwonik ki itilize frekans radyo (RF).'Q' mezire ki jan byen yon sikwi minimize pèt enèj...sou 1970/01/1 63043

-

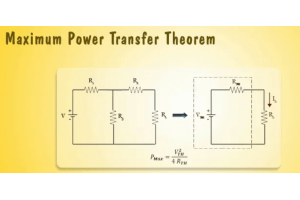

Atenn pèfòmans pik ak teyorèm nan transfè pouvwa maksimòm

Teyorèm maksimòm transfè pouvwa a eksplike kijan enèji ki sòti nan yon sous, tankou yon batri oswa dèlko, ap koule nan yon chaj ki konekte.Li montre kondisyon an egzak kote chaj la resevwa pouvwa k...sou 1970/01/1 54097

-

Espesifikasyon batri A23 ak konpatibilite

Batri a A23 se yon ti, silenn ki gen fòm batri ak vòltaj segondè.Yo te rele tou 23a, 23AE, oswa MN21, li kouri nan 12 vòlt ak pi wo pase AA oswa AAA pil.Konsepsyon espesyal li fè li pafè p...sou 1970/01/1 52197