EP1C4F400C8 FPGA: Karakteristik, espesifikasyon, pwogramasyon ak altènativ

Si ou ap travay ak lojik pwogramasyon, EP1C4F400C8 a ba ou yon balans pratik nan pèfòmans ak pri.Nan atik sa a, ou pral aprann ki sa FPGA sa a se, karakteristik kle li yo tankou kapasite lojik, memwa, ak I/O opsyon, ak ki jan estrikti li yo sipòte konsepsyon serye.Ou pral wè tou espesifikasyon li yo, aplikasyon pou nan sistèm, pwosesis pwogramasyon, ak ki jan li konpare ak pati menm jan an.Katalòg

Ki sa ki EP1C4F400C8 la?

A EP1C4F400C8 se yon manm nan Intel a (ansyen Altera a) fanmi Cyclone FPGA, ki fèt tankou yon solisyon pri-efikas ak serye pwogramasyon lojik.Bati sou yon pwosesis SRAM 0.13 µM, aparèy sa a ofri dansite lojik modere ak opsyon fleksib I/O nan yon pake kontra enfòmèl ant FBGA-400.Fanmi an Cyclone, ki gen ladan aparèy tankou EP1C3, EP1C6, EP1C12, ak EP1C20, te kreye balans pèfòmans ak aksesibilite pou desen évolutive, sa ki pèmèt migrasyon fasil ant nivo dansite ak pakè.Li te ye pou estabilite ak gwo adopsyon, li rete yon chwa ou fè konfyans nan desen eritaj.

Kap chèche EP1C4F400C8?Kontakte nou yo tcheke stock aktyèl, tan plon, ak prix.

EP1C4F400C8 CAD Modèl

EP1C4F400C8 senbòl

EP1C4F400C8 anprint

EP1C4F400C8 3D modèl

EP1C4F400C8 Karakteristik

• Kapasite lojik

EP1C4F400C8 a ofri alantou 4,000 eleman lojik, òganize nan 400 blòk etalaj lojik (Labs).Sa fè li apwopriye pou mitan-ranje desen ki mande pou modere dansite lojik pandan y ap kenbe efikasite pri.

• Embedded memwa

Li entegre apeprè 76.5 Kbits nan memwa entegre.RAM entèn sa a sipòte done tampon, depo, ak ti fonksyon memwa, diminye bezwen an pou eleman memwa ekstèn nan desen anpil.

• Segondè I/O konte

Aparèy la bay 301 itilizatè-configurable I/O broch nan pake 400-boul li yo FBGA.Sa a konte PIN segondè pèmèt koneksyon rich pou sistèm konplèks ki mande miltip interfaces periferik.

• Lajè mwen/o estanda sipò

Li sipòte plizyè estanda I/O ki gen ladan LVTTL, LVCMOS, SSTL-2, SSTL-3, ak LVD diferans.Fleksibilite sa a pèmèt FPGA a koòdone dirèkteman ak yon varyete de fanmi lojik modèn ak aparèy memwa.

• High-vitès diferans siyal

Avèk LVDS sipòte jiska 640 Mbps, FPGA a manch vit done transfè kondisyon.Sa fè li pratik pou aplikasyon pou tankou lyen kominikasyon gwo vitès ak vit interfaces dijital.

• Jesyon revèy ak PLLS

Chip la entegre de faz-fèmen pasan (PLLs) ak uit rezo revèy mondyal.Karakteristik sa yo pèmèt egzak jenerasyon revèy, miltiplikasyon, ak kontwòl jitter pou aplikasyon pou distribisyon-kritik.

• Low-vòltaj operasyon debaz

Opere nan yon nominal 1.5 V nwayo vòltaj, aparèy la balans pèfòmans ak pi ba konsomasyon pouvwa.Nivo vòltaj sa a te optimisé pou teknoloji CMOS 0.13-µM yo itilize nan fabwikasyon li.

• Fleksib I/O tension

FPGA a sipòte I/O tension nan 1.5 V, 1.8 V, 2.5 V, ak 3.3 V atravè bank diferan.Sa a adaptabilite pèmèt li nan koòdone ak tou de eritaj ak eleman sistèm modèn.

• SRAM ki baze sou konfigirasyon

Menm jan ak lòt siklòn FPGAs, li se SRAM ki baze sou epi li mande pou rkonfigurasyon nan tout pouvwa-up.Sa a bay fleksibilite pou dènye enfòmasyon, men tou li nesesè yon aparèy konfigirasyon ekstèn oswa kontwolè.

• Sipò konpresyon Bitstream

EP1C4F400C8 la sipòte konprese loading bitstream pandan konfigirasyon.Sa a diminye kondisyon memwa ekstèn ak vitès moute fwa konfigirasyon.

• Konfòmite psi

Li gen ladan l bati-an sipò pou estanda PCI (33/66 megaèrts, 32/64-ti jan).Karakteristik sa a pèmèt aparèy la yo dwe dirèkteman entegre nan sistèm ki mande PCI entèfas san yo pa plis lojik pon.

Estrikti laboratwa siklòn

Dyagram nan montre blòk la etalaj lojik (Laboratwa) estrikti yo itilize nan siklòn FPGAs tankou EP1C4F400C8 la.Chak laboratwa konekte nan yon rezo nan konekte: ranje konekte, kolòn konekte, ak konekte lokal yo, ki siyal wout ant eleman lojik ak lòt blòk.Direktè lyen dirèk bay vit, ki ba-latansi chemen nan laboratwa adjasan, amelyore pèfòmans distribisyon nan chemen siyal.Achitekti sa a enpòtan paske li balanse fleksibilite routage ak efikasite, pèmèt FPGA a okipe desen konplèks pandan y ap kenbe vitès ak zòn optimisé.

Cyclone I/O Banks Dyagram

Dyagram lan montre estrikti labank I/O nan siklòn FPGAs tankou EP1C4F400C8 la.Se aparèy la divize an kat I/O bank yo, chak patrone pa otobis pwòp ekipman pou li yo, sa ki pèmèt yo melanje diferan estanda vòltaj nan yon sèl FPGA.Tout bank sipòte nan yon pakèt domèn I/O estanda ki gen ladan LVTTL, LVCMOS, LVDS, RSDs, ak SSTL, pandan y ap Banks 1 ak 3 tou sipòte 3.3-V PCI pou konpatibilite ak sistèm eritaj.Sa a achitekti fleksib I/O enpòtan paske li pèmèt entegrasyon san pwoblèm ak divès aparèy ekstèn ak interfaces, fè FPGA a adaptab nan aplikasyon pou divès kalite.

EP1C4F400C8 Espesifikasyon

|

Lèt |

Paramèt |

|

Fabrikan |

Altera/Intel |

|

Seri |

Cyclone® |

|

Anbalaj |

Plato |

|

Estati pati |

Demode |

|

Kantite laboratwa/CLBS |

400 |

|

Kantite eleman lojik/selil |

4000 |

|

Total Bits Ram |

78,336 |

|

Kantite I/O |

301 |

|

Vòltaj - Pwovizyon pou |

1.425V ~ 1.575V |

|

Kalite aliye |

Sifas mòn |

|

Tanperati opere |

0 ° C ~ 85 ° C (TJ) |

|

Pake / Ka |

400-BGA |

|

Pake aparèy founisè |

400-FBGA (21 × 21) |

|

Nimewo pwodwi baz |

Ep1c4 |

EP1C4F400C8 aplikasyon

1. Processing siyal dijital (DSP)

EP1C4F400C8 a ka pwograme pou fè travay tankou filtraj, FFTs, ak batman siyal.Konbinezon li yo nan eleman lojik ak memwa entegre fè li apwopriye pou pwosesis segondè-vitès.Sa a pèmèt li ranplase bato DSP tradisyonèl ak yon solisyon FPGA fleksib ki ka reprogramasyon pou algoritm diferan.

2. Sistèm entegre ak kontwòl

Nan sistèm endistriyèl ak entegre, se FPGA sa a souvan itilize aplike contrôleur koutim, sekansyèl, ak machin eta a.Lojik reconfigurable li yo pèmèt yo tayè konpòtman pyès ki nan konpitè jisteman nan bezwen sistèm lan.Pa entegre lojik kontwòl andedan FPGA a, se nimewo a nan eleman ekstèn redwi, amelyore fyab ak pri bese.

3. Kominikasyon ak koòdone Tranzisyon

Aparèy la sipòte miltip I/O estanda epi yo ka aji kòm yon pon ant pwotokòl kominikasyon diferan.Li se souvan itilize konekte PCI, LVD, SDRAM, ak lòt interfaces transparans nan yon sistèm.Sa fè li trè itil nan ekipman rezo, entegre contrôleur, ak eritaj-a-modèn konvèsyon koòdone.

4. Done akizisyon ak Processing

Avèk segondè I/O disponiblite ak memwa fleksib, EP1C4F400C8 a se byen adapte pou sistèm koleksyon done yo.Li ka dirèkteman koòdone ak ADCs ak detèktè, pwosesis done yo nan tan, ak prepare li pou depo oswa transmisyon.Aplikasyon sa yo komen nan enstriman medikal, ekipman tès, ak aparèy mezi syantifik.

Ep1c4f400c8 pati ki sanble

|

Spesifikasyon |

EP1C4F400C8 |

Ep1c4f400c8n |

EP1C4F400C8NAA |

Ep1c4f400c6n |

Ep1c4f324c8n |

Ep1c4t144c8n |

|

Fabrikan |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

|

Fanmi FPGA |

Cyclone (EP1C4) |

Cyclone (EP1C4) |

Cyclone (EP1C4) |

Cyclone (EP1C4) |

Cyclone (EP1C4) |

Cyclone (EP1C4) |

|

Eleman lojik (les) |

4,000 |

4,000 |

4,000 |

4,000 |

4,000 |

4,000 |

|

Embedded memwa (Bits) |

~ 76.5 Kbits |

~ 76.5 Kbits |

~ 76.5 Kbits |

~ 76.5 Kbits |

~ 76.5 Kbits |

~ 76.5 Kbits |

|

Mwen/o broch |

301 |

301 |

301 |

301 |

249 |

97 |

|

Pake / Ka |

400-FBGA |

400-FBGA |

400-FBGA |

400-FBGA |

324-FBGA |

144-TQFP |

|

Vitès |

C8 |

C8 |

C8 |

C6 (pi vit) |

C8 |

C8 |

|

Nwayo vòltaj |

1.5 V |

1.5 V |

1.5 V |

1.5 V |

1.5 V |

1.5 V |

|

Operating Temp.Distans |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C

|

EP1C4F400C8 etap pwogramasyon

Anvan ou ka itilize EP1C4F400C8 FPGA a, ou dwe chaje konsepsyon ou nan aparèy la.Pwogramasyon enplike nan konfigirasyon FPGA a ak yon dosye Bitstream konsa li konnen ki jan yo konpòte yo kòm sikwi gen entansyon ou.

1. Chwazi konplo konfigirasyon & mete broch MSEL

Ou kòmanse pa chwazi konplo a konfigirasyon ki pi byen adapte konfigirasyon ou a, tankou seri aktif, seri pasif, oswa JTAG.Sa a se fè pa mete broch yo MSEL nan nivo lojik espesifik anvan pouvwa-up.Chak mòd sèvi ak broch diferan ak pwotokòl, kidonk ou bezwen konfime konpatibilite ak zouti konsepsyon ou ak memwa konfigirasyon.Fè bon chwa a isit la asire yon pwosesis konfigirasyon lis.

2. Aplike pouvwa & inisyalize aparèy la

Next, pouvwa moute nwayo FPGA a ak I/O ray nan chenn yo vòltaj espesifye.Pandan demaraj, kenbe PIN la NCONFIG ki ba yo kenbe aparèy la nan Reyajiste jiskaske tension yo ekipman pou yo ki estab.Yon fwa ki estab, ou lage Reyajiste ak aparèy la siyal preparasyon pou pa kondwi PIN la NSTATUS.Sa a garanti FPGA a byen inisyalize anvan konfigirasyon kòmanse.

3. Transmèt konfigirasyon Bitstream la

Nan faz sa a, ou voye dosye a done konfigirasyon (bitstream) nan FPGA a lè l sèvi avèk konplo chwazi ou.Nan aktif seri oswa pasif mòd seri, Bitstream a soti nan yon aparèy memwa ekstèn, pandan y ap JTAG pèmèt pwogram dirèk via kab.Aparèy la kontinyèlman li nan done yo konfigirasyon jiskaske li a konplè.Lojisyèl konsepsyon ou jenere sa a Bitstream matche ak kondisyon lojik ou.

1. Konfime konfigirasyon siksè (conf_done)

Lè FPGA a fini loading, li pretann PIN la conf_done yo montre ke done konfigirasyon te avèk siksè resevwa.An menm tan an, aparèy la fè inisyalizasyon entèn tankou netwaye anrejistre ak aktive I/O.Si conf_done echwe yo ale segondè, li anjeneral vle di done yo konfigirasyon oswa konfigirasyon gen yon erè.Gade PIN sa a se fason ki pi senp lan pou verifye pwosesis la konplè.

5. Fè si ou vle nan-sistèm rkonfigurasyon

Finalman, ou gen opsyon pou mete ajou oswa rprograme FPGA a san yo pa retire li nan tablo a.Sèvi ak JTAG oswa yon kontwolè entegre, ou ka chaje yon nouvo Bitstream dirèkteman, ki se itil pou dènye mikrolojisyèl.Fleksibilite sa a pèmèt ou modifye, debug, oswa ajou sistèm ou menm apre deplwaman.Li asire konsepsyon FPGA ki baze sou ou ka adapte sou tan a chanje kondisyon.

EP1C4F400C8 avantaj ak dezavantaj

Avantaj

• Pri-efikas chwa pou mitan-ranje desen

• Segondè konte I/O konpare ak aparèy dansite menm jan an

• Vòltaj fleksib ak sipò estanda I/O

• Te apiye nan zouti ki gen matirite ak dokiman yo

• Pi ba itilize pouvwa pase pi gran jenerasyon FPGA

Dezavantaj

• demode ak disponiblite alontèm limite

• Lower lojik ak memwa kapasite vs modèn FPGAs

• Pi dousman vitès opere ak I/O pèfòmans

• Mande pou memwa ekstèn pou konfigirasyon sou pouvwa-up

• manke karakteristik avanse tankou blòk DSP ak resèpteur gwo vitès

Ep1c4f400c8 dimansyon anbalaj

|

Lèt |

Paramèt |

|

Kalite pake |

Fbga (amann-pitch boul etalaj) |

|

Boul konte |

400 |

|

Boul boul (e) |

1.0 mm (tipik pou siklòn EP1C4F400) |

|

Dyamèt boul (b) |

0.45 mm (nominal) |

|

Gwosè pake (d × e) |

21 mm × 21 mm |

|

Pake wotè (a) |

2.40 mm (max) |

|

Epesè substrate (a2) |

~ 0.40 mm |

|

Epesè bouchon mwazi (A3) |

~ 1.90 mm |

|

Wotè boul (A1) |

0.25 mm (nominal) |

|

PIN A1 Corner |

Make pou oryantasyon |

|

Layout etalaj |

20 × 20 griy (ak voye boul kwen ki manke) |

|

Aliye |

Mount sifas (SMD) |

EP1C4F400C8 manifakti

EP1C4F400C8 a te orijinèlman manifaktire pa Altera Corporation, yon pyonye nan aparèy lojik pwogramasyon ak teknoloji FPGA.Nan 2015, Altera te rann pa Intel Corporation, ak liy lan pwodwi te vin yon pati nan Intel a pwogramasyon solisyon gwoup (PSG).Jodi a, Intel sipòte sa yo eritaj aparèy Altera pandan y ap konsantre devlopman sou plus fanmi FPGA, asire kontinwite pou itilizatè ki egziste deja ak avanse inovasyon nan lojik pwogramasyon.

Konklizyon

EP1C4F400C8 a vle di soti kòm yon pri-efikas ak versatile FPGA ki ofri pèfòmans solid pou mitan-ranje desen.Avèk 4,000 eleman lojik li yo, memwa entegre, anpil sipò I/O, ak konpatibilite ak plizyè vòltaj ak estanda koòdone, li bay fleksibilite nan tout aplikasyon varye.Achitèk li yo, pwosesis pwogramasyon, ak gwo itilizasyon nan DSP, sistèm entegre, ak akizisyon done fè li yon chwa pratik malgre estati eritaj li yo.Pandan ke li manke karakteristik avanse yo te jwenn nan plus aparèy ak ap fè fas limite disponiblite alontèm, li rete yon opsyon serye k ap chèche solisyon pwouve nan évolutive desen FPGA.

Fich pdf

EP1C4F400C8 fich:

Sou nou

ALLELCO LIMITED

Li piplis

Quick Inquiry

Tanpri voye yon ankèt, nou pral reponn imedyatman.

Kesyon yo poze souvan [FAQ]

1. Ki zouti ki nesesè pou pwogram EP1C4F400C8 la?

Ou bezwen lojisyèl Quartus Intel a (deja Altera Quartus II) ansanm ak yon kab pwogramasyon sipòte tankou USB-Blaster.Zouti sa yo pèmèt ou kreye Bitstream la ak chaje li nan FPGA la.

2. Èske EP1C4F400C8 okipe aplikasyon yo dirèkteman?

Wi, li te bati-an konfòmite pou estanda psi (33/66 megaèrts, 32/64-ti jan), fè li apwopriye pou pci ki baze sou sistèm entegrasyon san yo pa egzije siplemantè lojik pon.

3. Kisa k ap pase si EP1C4F400C8 a echwe pandan konfigirasyon?

Si konfigirasyon echwe, PIN la conf_done pa pral afime segondè.Sa a anjeneral pwen nan yon erè nan dosye a Bitstream, sekans vòltaj, oswa konfigirasyon PIN, epi yo ta dwe verifye nan koule konsepsyon ou.

4. Èske koòdone nan EP1C4F400C8 dirèkteman ak memwa DDR?

Li sipòte plizyè estanda I/O men li pa gen interfaces natif natal DDR tankou FPGA modèn.Konsiderasyon konsepsyon adisyonèl oswa konpozan Tranzisyon ka nesesè.

5. Ki jan EP1C4F400C8 la konpare ak plus FPGAs?

Konpare ak aparèy modèn, EP1C4F400C8 a gen pi ba vitès, mwens dansite lojik, ak mwens karakteristik avanse.Sepandan, li rete yon chwa pri-efikas pou ki estab, mitan-ranje desen kote pèfòmans dènye kri pa obligatwa.

EPM3256AFC256-7 CPLD Apèsi sou lekòl la: Karakteristik, pinout, pwogramasyon ak aplikasyon pou

sou 2025/10/3

ADG432BR Analog switch IC: Espesifikasyon, pinout, altènativ ak fich

sou 2025/10/2

Posts popilè

-

Enstriksyon konplèks Set Odinatè: Ki jan yo chanje informatique?

sou 8000/04/18 147771

-

USB-C pinout ak karakteristik

sou 2000/04/18 112009

-

Sèvi ak Xilinx Inifye Simulation Primitif: Yon Gid konplè nan FPGA Design ak Simulation

sou 1600/04/18 111351

-

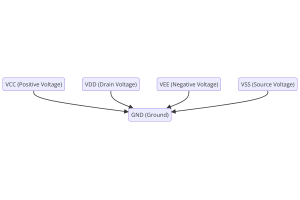

Tansyon ekipman pou pouvwa nan elektwonik: siyifikasyon VCC, VDD, VEE, VSS, ak GND

sou 0400/04/18 83768

-

RJ45 Connector Gid: Pinout, fil elektrik, Kalite Kab, ak Itilizasyon

sou 1970/01/1 79565

-

Gid la ultim nan kòd koulè fil nan sistèm elektrik modèn

Fason sistèm elektrik nou yo itilize koulè yo pa sèlman pou sanble.Chak koulè fil kounye a endike yon fonksyon espesifik, fè li pi fasil yo idantifye ak okipe konpozan elektrik kòrèkteman pandan en...sou 1970/01/1 66960

-

Purge Valv Gid: Fonksyon, sentòm, tès, ak ranplasman pou pèfòmans motè optimal

Valv la weteur se yon pati enpòtan nan sistèm yon machin nan ki ede kenbe lè a pwòp pa jere vapè gaz yo anvan yo ka chape anba nan atmosfè a.Sa a pa sèlman ede anviwònman an pa diminye polisyon, me...sou 1970/01/1 63098

-

Kalite (q) Faktè: Ekwasyon ak aplikasyon

Faktè bon jan kalite a, oswa 'Q', se enpòtan lè tcheke ki jan byen endukteur ak rezonan travay nan sistèm elektwonik ki itilize frekans radyo (RF).'Q' mezire ki jan byen yon sikwi minimize pèt enèj...sou 1970/01/1 63040

-

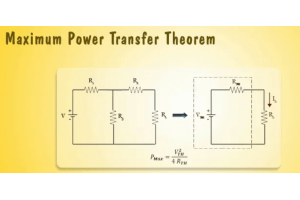

Atenn pèfòmans pik ak teyorèm nan transfè pouvwa maksimòm

Teyorèm maksimòm transfè pouvwa a eksplike kijan enèji ki sòti nan yon sous, tankou yon batri oswa dèlko, ap koule nan yon chaj ki konekte.Li montre kondisyon an egzak kote chaj la resevwa pouvwa k...sou 1970/01/1 54097

-

Espesifikasyon batri A23 ak konpatibilite

Batri a A23 se yon ti, silenn ki gen fòm batri ak vòltaj segondè.Yo te rele tou 23a, 23AE, oswa MN21, li kouri nan 12 vòlt ak pi wo pase AA oswa AAA pil.Konsepsyon espesyal li fè li pafè p...sou 1970/01/1 52184