EPF6016ATC144-2N FPGA: Karakteristik, pwogramasyon, aplikasyon, ak altènativ

Gid sa a se tout sou EPF6016ATC144-2N a, yon kalite chip rele yon FPGA.Yo itilize li nan sistèm dijital ki bezwen fleksib ak fasil pou mete ajou.Gid la eksplike ki sa chip la fè, ki jan li fonksyone, pati prensipal li yo ak karakteristik, ki jan yo sèvi ak ak pwogram li, kote li ka itilize, e poukisa li la toujou yon bon chwa jodi a.Katalòg

Ki sa ki EPF6016ATC144-2N a?

A EPF6016ATC144-2N se yon manm nan Flex 6000 fanmi an FPGA devlope pa Altera, kounye a yon pati nan Intel.Bati sou SRAM ki baze sou reprogramabl lojik, se aparèy sa a Enjenieri pou fleksibilite nan mitan-dansite aplikasyon pou lojik dijital.Li tire achitekti a OptifLex, ki konbine blòk etalaj lojik (Labs) ak yon gwo vitès matris entèrkonèkte delivre itilizasyon resous efikas ak rapid siyal routage.EPF6016ATC144-2N sipòte nan-sistèm rkonfigurasyon, fè li ideyal pou desen ki mande dènye oswa modifikasyon pòs-deplwaman.Kòm yon pati nan seri a Flex 6000, li ofri yon solisyon pri-efikas pou ranplase ranje pòtay tradisyonèl pandan y ap senplifye sik la devlopman.

Kap chèche EPF6016ATC144-2N?Kontakte nou yo tcheke stock aktyèl, tan plon, ak prix.

EPF6016ATC144-2N CAD modèl

EPF6016ATC144-2N senbòl

EPF6016ATC144-2N

EPF6016ATC144-2N 3D modèl

EPF6016ATC144-2N karakteristik

• Kapasite lojik

EPF6016ATC144-2N a ofri alantou 16,000 pòtay sistèm, aplike lè l sèvi avèk 1,320 eleman lojik (LES) atravè 132 blòk etalaj lojik (Labs).Sa a bay konpleksite modere apwopriye pou aplikasyon pou mitan-ranje FPGA.

• Mwen/o broch

Li sipòte jiska 117 itilizatè-configurable I/O broch.Sa yo broch pèmèt koneksyon fleksib nan konpozan sistèm divès kalite ak aparèy ekstèn.

• Nwayo vòltaj

Nwayo a opere nan 3.3V ak yon seri fonksyonèl soti nan 3.0V 3.6V. Sa a pèmèt konpatibilite ak estanda ki ba-vòltaj sistèm dijital.

• Mwen/o vòltaj

Karakteristik multivolt I/O li yo sipòte entèfas ak aparèy lè l sèvi avèk 3.3V oswa 2.5V nivo.Sa a senplifye entegrasyon nan anviwònman melanje-vòltaj.

• Tanperati opere

Estanda fonksyònman junction ranje a se 0 ° C a +85 ° C.Sa a sipòte anviwònman tipik komèsyal ak endistriyèl.

• Pwovizyon pou aktyèl

Li trase apeprè 5mA pandan operasyon nòmal ak mwens pase 0.5mA nan mòd ki sibstiti an.Sa a ede konsève pouvwa nan enèji-konsyan desen.

• Vitès revèy (vitès klas –2n)

Avèk yon klas vitès –2, li reyalize frekans lojik entèn jiska apeprè 166MHz.Sa a pèmèt kalkil vit nan pwosesis siyal oswa lojik kontwòl.

• Achitekti

Baze sou achitekti Optiflex Altera a, li itilize LUT ki baze sou lojik ak resous dedye routage.Achitekti sa a ofri gwo dansite lojik ak pèfòmans efikas.

• Fasttrack konekte

FastTrack routage kadriyaj la pèmèt ba-latency chemen siyal ak sipòte transfè done gwo vitès atravè blòk lojik.Sa a kontribye nan distribisyon ki konsistan ak pèfòmans.

• Nan-sikwi rkonfigurasyon

Li itilize SRAM ki baze sou konfigirasyon lojik, sa ki pèmèt FPGA a yo dwe reprogramasyon nan-sistèm.Sa a sipòte dènye konsepsyon oswa adaptasyon pyès ki nan konpitè dinamik san yo pa retire li.

• Eskanè fwontyè jtag

Aparèy la gen ladan IEEE 1149.1-konfòme JTAG Boundary-eskanè lojik.Sa a fasilite debogaj ak nan-sistèm testabilite nan tablo ak konekte.

• Sipò cho-kou.

Li ka san danje mete oswa retire pandan y ap mache nan sistèm 3.3V.Karakteristik sa a se itil nan tribin kenkayri modilè oswa reparabl.

• Tès fonksyonèl

Chak inite konplètman fonksyone teste anvan chajman.Sa a asire bon jan kalite ak elimine bezwen pou itilizatè-defini vektè tès pandan devlopman.

• PCI konpatibilite

Aparèy la se konpatib ak PCI revizyon otobis lokal 2.2 pou operasyon 5V.Sa a pèmèt li itilize nan eritaj ki baze sou sistèm entegre.

OptifLex Achitekti blòk Dyagram

Dyagram nan montre ki jan pati entèn yo nan FPGA a yo òganize ak konekte.Nan sant la yo se blòk etalaj lojik (laboratwa), sa yo, se inite yo bilding prensipal nan chip la.Chak laboratwa gen plizyè eleman lojik (LES) ki fè operasyon debaz yo dijital, tankou pòtay lojik ak baskile-flops.Laboratwa yo ki konekte ak yon konekte lokal yo, ki pèmèt lojik la andedan chak blòk yo travay ansanm avèk efikasite.Pou pi laj kominikasyon atravè chip a, laboratwa yo ap mennen nan ranje ak kolòn FastTrack entèrkonèkte, chemen vit siyal ki kite done deplase byen vit soti nan yon pati nan chip a nan yon lòt ak reta ki ba.Anviwon bor yo deyò nan dyagram lan yo se eleman yo opinyon/pwodiksyon (IOES).Sa yo konekte lojik entèn FPGA a nan aparèy ekstèn pa konvèti ant nivo lojik ChIP a ak nivo yo vòltaj itilize pa lòt pyès ki nan konpitè.Layout sa a, ak blòk modilè li yo ak gwo vitès chemen routage, reflete fleksibilite a ak konsantre pèfòmans nan achitekti a Optiflex.

Flex 6000 modèl distribisyon

Flex 6000 modèl la distribisyon montre ki jan siyal deplase epi yo reta jan yo vwayaje nan FPGA la.Nan sant la nan modèl la yo se eleman lojik (LES), ki pwosesis done ak siyal kontwòl ak distribisyon espesifik.Chak LE konekte nan chemen distribisyon tankou T_DATA_TO_REG ak T_REG_TO_OUT, ki defini konbyen tan li pran pou siyal yo antre nan, dwe trete, ak sòti lojik la.

Bòkote LES yo se chemen espesyal yo rele laboratwa pote ak laboratwa cascade.Sa yo pèmèt siyal pou avanse pou pi orizontal ant eleman lojik nan blòk la menm, sipòte operasyon vit tankou ajoute ak konparezon.Chemen sa yo gen valè distribisyon pwòp yo, tankou T_CARRY_TO_REG ak T_CASC_TO_OUT, ki mezire reta pandan operasyon sa yo.

Nan pati anba a nan dyagram lan, eleman yo opinyon/pwodiksyon (IOES) okipe siyal pral nan ak soti nan chip la.Yo enkli pwen reta tankou T_IN_DELAY, ki konte pou varyasyon lè yo ap resevwa done ki sòti nan aparèy ekstèn.

Modèl la gen ladan tou chemen routage nan diferan nivo (t_local, t_row, t_col, ak t_global) chak ki reprezante ki jan lwen yon siyal vwayaje ak konbyen tan li pran.Chemen sa yo ede konprann ak jere reta nan tout diferan pati nan chip a, fè li pi fasil yo satisfè pèfòmans ak objektif distribisyon.

EPF6016ATC144-2N Espesifikasyon

|

Lèt |

Paramèt |

|

Fabrikan |

Altera/Intel |

|

Seri |

Flex 6000 |

|

Anbalaj |

Plato |

|

Estati pati |

Demode |

|

Kantite laboratwa/CLBS |

132 |

|

Kantite eleman lojik/selil |

1320 |

|

Kantite I/O |

117 |

|

Kantite pòtay |

16000 |

|

Vòltaj - Pwovizyon pou |

3V ~ 3.6V |

|

Kalite aliye |

Sifas mòn |

|

Tanperati opere |

0 ° C ~ 85 ° C (TJ) |

|

Pake / Ka |

144-LQFP |

|

Pake aparèy founisè |

144-TQFP (20x20) |

|

Nimewo pwodwi baz |

EPF6016 |

EPF6016ATC144-2N

1. Travay siyal dijital (DSP) travay

Avèk 1,320 eleman lojik ak vit entèrkonèkte, EPF6016ATC144-2N a sipòte aplikasyon an nan ti nan mitan-ranje fonksyon siyal dijital pwosesis.Li kapab itilize yo kreye filtè Custom FIR, FFT am, oswa paralèl lojik aritmetik pou transfòmasyon siyal.Malgre ke li manke dedye blòk DSP oswa multiplicateurs entegre, lojik jeneral-bi li yo ka okipe repetitif miltipliye-akimile operasyon apwopriye pou entegre pwosesis odyo, Capteur done filtraj, ak ond mete nan kontwòl oswa sistèm kominikasyon.

2. Embedded kontwòl ak automatisation endistriyèl

Aparèy la se byen adapte pou aplikasyon pou kontwòl entegre nan anviwònman endistriyèl.Kapasite li nan koòdone ak melanje-vòltaj I/O (2.5 V ak 3.3 V), operasyon ki estab li yo anba estanda tanperati komèsyal (0-85 ° C), ak sipò pou cho-kou.Rekonfigurabilite a pèmèt pou fleksibilite pwodwi alontèm, kote yo ka mete ajou lojik san yo pa ranplase pyès ki nan konpitè.

3. Kominikasyon Pwotokòl Tranzisyon ak lojik koòdone

Mèsi a multivolt I/O sipò li yo ak efikas rezo routage, EPF6016ATC144-2N a ka itilize aplike interfaces kominikasyon koutim ak konvètisè pwotokòl.Li ka bati UARTS, Contrôleur SPI, oswa tradiktè otobis paralèl yo ki ap pèmèt entèraksyon ant sistèm dijital mismatched.Konte modere I/O li yo (117 GPIOs) ak jesyon revèy entèn tou sipòte siyal tan-sansib, fè li apwopriye pou ekipman rezo, imitasyon otobis eritaj, oswa kòm yon eleman lojik lakòl nan pi gwo sistèm kominikasyon done.

4. Komisyon Konsèy-nivo tès, debogaj, ak validasyon

Avèk bati-an JTAG fwontyè-eskanè kapasite (IEEE 1149.1 konfòme), EPF6016ATC144-2N a sipòte avanse tablo-nivo tès san yo pa egzije sond ekstèn lojik oswa diagnostics pèsistan.Li ka verifye koneksyon I/O, detekte sikwi louvri oswa kout, ak fè chèk nan-sistèm pandan pwodiksyon oswa antretyen jaden.Karakteristik sa a se itil nan konplèks multilayer PCB oswa nan sistèm kote aksè tradisyonèl nan pwen tès yo limite oswa Inposibl.

EPF6016ATC144-2N Pati ki sanble

|

Karakteristik |

EPF6016ATC100-1 |

EPF6016ATC100-3N |

EPF6016ATC144-3N |

|

Fabrikan |

Altera |

Intel (Altera Legacy) |

Intel (Altera Legacy) |

|

Fanmi |

Flex 6000 |

Flex 6000 |

Flex 6000 |

|

Eleman lojik (les) |

1,320 |

1,320 |

1,320 |

|

Konte Gate (approx.) |

16,000 |

16,000 |

16,000 |

|

Pakèt |

100-PIN TQFP |

100-PIN TQFP |

144-PIN TQFP |

|

Itilizatè mwen/O broch |

81 |

81 |

117 |

|

Vitès |

-1 (estanda) |

-3n (gwo vitès) |

-3n (gwo vitès) |

|

Max frekans revèy |

Pi ba (tipikman ~ 100 megaèrts) |

Pi wo (jiska ~ 166 megaèrts) |

Pi wo (jiska ~ 166 megaèrts) |

|

Kalite konfigirasyon |

SRAM ki baze sou |

SRAM ki baze sou |

SRAM ki baze sou |

|

Pouvwa ekipman pou vòltaj |

3.3 V |

3.3 V |

3.3 V |

|

Cho-kou. |

Wi |

Wi |

Wi |

|

Jtag/eskanè fwontyè |

Wi |

Wi |

Wi |

|

Aplikasyon |

Lojik debaz, desen kontra enfòmèl ant |

Pi vit lojik kontwòl, kontra enfòmèl ant |

Sistèm pèfòmans ki wo, plis I/O |

|

Disponibilite |

Demode |

Demode |

Demode |

EPF6016ATC144-2N etap pwogramasyon

1. Chwazi mòd konfigirasyon an

EPF6016ATC144-2N a sipòte konfigirasyon SRAM ki baze sou, sa vle di li mande pou pwogramasyon sou tout pouvwa-up.Aparèy la pèmèt pou plizyè rapid konfigirasyon, pi souvan pasif seri (PS) ak pasif paralèl asenkron (PPA).Se mòd nan konfigirasyon detèmine pa ki jan PIN la MSEL konekte.Pou egzanp, lè MSEL se mare ki ba, aparèy la espere done yo dwe voye seri via EEPROM ekstèn (tankou EPC1) oswa yon kab download.Chwazi metòd la konfigirasyon kòrèk depann sou konsepsyon nan sistèm, EEPROM ki baze sou pou otomatik bòt-up, oswa kab ki baze sou pou prototip ak tès yo.

2. Konpile konsepsyon an FPGA ak jenere yon dosye pwogramasyon

Pou pwogram FPGA a, ou dwe premye kreye konsepsyon pyès ki nan konpitè ou lè l sèvi avèk Intel a Quartus oswa Legacy Max+Plus II lojisyèl konsepsyon.Apre konpilasyon, zouti a jenere yon SOF (SRAM dosye objè) ki reprezante lojik la configuré.Sa a SOF dwe Lè sa a, dwe konvèti nan yon fòma konpatib ak metòd konfigirasyon ou chwazi a:

• .rbf oswa .pof pou aparèy EEPROM (eg, EPC1).

• .ttf oswa .Hex pou mikrokontroleur oswa paralèl loading.

Se konvèsyon an fè lè l sèvi avèk bati-an dosye sèvis piblik la konvètisè nan lojisyèl an konsepsyon.Etap sa a asire ke se Bitstream a fòma kòrèkteman pou FPGA a entèprete.

3. Pwogram memwa konfigirasyon an (si w ap itilize EEPROM)

Nan aplikasyon kote yo itilize yon aparèy konfigirasyon seri tankou yon EPC1, pwochen etap la se chaje done yo konfigirasyon nan EEPROM la.Sa a se tipikman fè lè l sèvi avèk yon zouti pwogramasyon Desktop (eg, MAX+Plus II pwogramè oswa pwogramè Quartus).Pwosesis la enplike nan mete EEPROM a nan yon priz pwogramasyon oswa konekte li nan-sikwi, chaje dosye a pwogramasyon ki apwopriye (anjeneral .pof oswa .rbf), ak kòmanse sik la pwogram lan.Yon fwa pwograme, EEPROM a pral otomatikman bay done yo konfigirasyon nan FPGA a chak fwa sistèm nan pouvwa moute, elimine bezwen pou rprogramasyon manyèl.

4. Configured lè l sèvi avèk yon kab download (pasif seri)

Yon altènativ a EEPROM ki baze sou bòt-up se lè l sèvi avèk yon kab download (tankou USB-Blaster oswa byteblaster) dirèkteman configured FPGA la.Nan metòd sa a, ou konekte kab la nan PC ou ak Nconfig FPGA a, DCLK, done, ak broch conf_done.Sèvi ak pwogramè a Quartus, ou kòmanse pwosesis la konfigirasyon, ki pulsasyon nconfig ki ba yo kòmanse.Zouti a Lè sa a, voye done yo konfigirasyon seri nan liy lan done, reusi pa DCLK.Pwosesis la se konplè lè conf_done ale segondè, ki endike konfigirasyon siksè ak tranzisyon aparèy la nan mòd itilizatè.

5. Configure lè l sèvi avèk yon mikrokontroleur (pasif seri/paralèl)

Si sistèm ou an sèvi ak yon mikrokontroleur entegre, li kapab tou aji kòm mèt konfigirasyon FPGA a.Nan konfigirasyon sa a, mikrokontroleur la afime Nconfig Low pou Reyajiste FPGA a, lè sa a orè konfigirasyon Bitstream a nan done pandan y ap baskile DCLK.Kondisyon pou distribisyon yo dwe respekte, tan konfigirasyon done anvan revèy la epi kenbe tan apre sa yo bon pou konfigirasyon siksè.Mikrokontroleur a ka kontwole broch yo NSTATUS ak CONF_DONE yo detekte erè konfigirasyon oswa konfime konplete avèk siksè.Metòd sa a ofri kontwòl konplè sou pwosesis la konfigirasyon ak sipòte dènye nouvèl sou dinamik nan jaden an.

6. Siveye siyal konfigirasyon

Pandan pwosesis la konfigirasyon, FPGA a bay fidbak nan broch estati:

• NSTATUS endike deteksyon erè;Li ale ba si yon fay rive (eg, erè CRC oswa vyolasyon distribisyon).

• conf_done ale segondè yon fwa tout Bits konfigirasyon yo avèk siksè chaje ak verifye.

Si NSTATUS rete segondè ak CONF_DONE tranzisyon segondè nan fen sekans lan, aparèy la otomatikman antre nan mòd itilizatè, kote itilizatè-defini lojik vin aktif.Siveyans siyal sa a enpòtan pou asire pwosesis pwogramasyon an konplete avèk siksè.

7. Fè rkonfigurasyon lè sa nesesè

Paske EPF6016ATC144-2N a se SRAM ki baze sou, li ka konfigure nan nenpòt ki lè pa baskile PIN la NCONFIG ki ba, ki retabli aparèy la ak rdemaraj sik la konfigirasyon.Karakteristik sa a pèmèt pou dènye sistèm fleksib ak chanjman pandan operasyon san ranplasman fizik.Kapasite nan rkonfigurasyon pandan y ap nan-sikwi tou sipòte èkse, dinamik echanj fonksyon, oswa korije pinèz pòs-deplwaman.Sa fè aparèy la trè apwopriye pou aplikasyon pou ki mande adaptabilite oswa lonjevite.

8. Obsève kondisyon distribisyon ak elektrik

Pwogramasyon EPF6016ATC144-2N a avèk siksè tou mande pou atansyon a kontrent elektrik ak distribisyon.Revèy la konfigirasyon (DCLK) dwe satisfè limit frekans (eg, tipikman jiska 10 megaèrts nan estanda mòd seri).Aparèy la mande pou yon reta kout (apeprè 200 ms) apre pouvwa-up pou entèn pouvwa-sou Reyajiste a estabilize.Anplis de sa, tout siyal konfigirasyon yo ta dwe pwòp, bri-gratis, ak byen sispann.Si w ap itilize cho-kou., yo dwe pran swen asire entegrite siyal ak sekans apwopriye nan pouvwa ak I/O.

EPF6016ATC144-2N avantaj

• Pri-efikas pou mitan-konpleksite desen

EPF6016ATC144-2N a frape yon balans ant aksesibilite ak fonctionnalités, fè li ideyal pou desen ki mande pou plis fleksibilite pase lojik fiks men pa jistifye depans lan oswa pouvwa sou tèt li nan-wo fen FPGAs.

• Senplifye konsepsyon PCB ak entegrasyon

Konpare ak pi wo-dansite FPGAs ki souvan mande pou amann-pitch pakè BGA, EPF6016ATC144-2N a vini nan yon estanda 144-PIN TQFP pake.Anbalaj sa a senplifye tou de konsepsyon an ak manifakti nan PCBs paske li evite bezwen an pou zouti Layout avanse, microvias, oswa koute chè-wo kouch-konte ankadreman.Li te tou fasilite men-soudi oswa debaz rivork, ki se benefis pou pi piti ekip oswa laboratwa ak kapasite asanble limite.

• Ba risk pou obsolesans pandan deplwaman

Akòz sipò depi lontan li yo nan aplikasyon pou Legacy Endistriyèl, EPF6016ATC144-2N rete disponib nan anpil mache segondè ak se toujou lajman sipòte nan lojisyèl konsepsyon tankou Quartus II ak Max+Plus II.Pou konpayi yo kenbe pwodwi long-lifekik tankou automatisation faktori, sistèm mezi, oswa modil telecom, sa a asire kontinye aksè a li te ye-bon Silisyòm san yo pa bezwen nan Redesign pyès ki nan konpitè alantou plus, pi konplèks FPGAs.

• Konpòtman serye

Kontrèman ak kèk plus-wo pèfòmans FPGAs ki opere nan marges sere epi yo sansib a pouvwa ak fluctuations tanperati, EPF6016ATC144-2N a se gaya ak toleran nan varyasyon komen nan anviwònman an.Li opere alèz atravè seri a tanperati komèsyal ak sipòte cho-kou., sa ki fè li serye nan sistèm modilè oswa reparabl.Sa a fyab fè li yon chwa pratik pou sistèm ki mande ki konsistan pèfòmans sou tan ak anba kondisyon varyab.

• Alontèm estabilite konsepsyon

Nan senaryo kote alontèm disponiblite ak konsepsyon friz yo pi enpòtan pase pèfòmans dènye kri, aparèy sa a se yon kandida solid.Yon fwa yo lojik la valide ak dosye a konfigirasyon fèmen desann, sistèm nan tout ka rete chanje pou ane, menm deseni.Sa a se yon gwo benefis nan aplikasyon pou avyon, transpò, ak militè kote rekalifikasyon nan pati nouvo se chè oswa Inposibl.

EPF6016ATC144-2N Dimansyon anbalaj

Kalite pake: TQFP-144 (mens kwadwilatè plat pake)

Gwosè kò: 20 mm × 20 mm

Anplasman PIN: 0.5 mm

Konte PIN: 144 broch

Wotè pake: 1.0 mm

Kalite ankadreman plon: Gull-zèl mennen sou tout kat kote yo

Kalite aliye: Sifas-mòn (SMT)

EPF6016ATC144-2N manifakti

EPF6016ATC144-2N a te orijinèlman manifaktire pa Altera Corporation, yon pyonye nan devlopman nan jaden-pwogramasyon ranje pòtay (FPGAs).Nan 2015, Altera te rann pa Intel Corporation, ak aparèy la se kounye a ofisyèlman ki nan lis anba gwoup solisyon pwogramasyon Intel a, ki jere ak sipòte Altera a eritaj liy pwodwi FPGA.Malgre ke EPF6016ATC144-2N a se yon pati nan yon fanmi sispann, Intel rete manifakti a fòmèl ak netwayè nan aparèy sa a, kenbe dokiman, sipò achiv, ak avi lifecycle anba mark la Intel.

Konklizyon

EPF6016ATC144-2N a se yon FPGA fleksib ak serye pou anpil pwojè diferan.Li ofri yon bon kantite lajan pou pouvwa lojik, anpil opinyon/pwodiksyon broch, ak fasil nan-sistèm dènye.Konsepsyon li yo sipòte sistèm melanje-vòltaj, vit mouvman done, ak reprogramasyon san yo pa retire li nan yon tablo.Li nan souvan yo itilize nan bagay sa yo tankou sistèm kontwòl, pwosesis siyal, lyen kominikasyon, ak ekipman tès la.Avèk sipò fò, disponiblite long, ak anbalaj senp, li rete yon chwa entelijan ki bezwen yon solisyon pri-efikas ak ki estab.

Fich pdf

EPF6016ATC144-2N fich:

Sou nou

ALLELCO LIMITED

Li piplis

Quick Inquiry

Tanpri voye yon ankèt, nou pral reponn imedyatman.

Kesyon yo poze souvan [FAQ]

1. Ki zouti mwen bezwen pou pwogram EPF6016ATC144-2N jodi a?

Ou ka itilize eritaj Intel a Quartus II oswa Max+Plus II lojisyèl pou devlopman ak konpilasyon.Pou pwogramasyon, zouti tankou USB-Blaster kab la ak pwogramè Quartus rete konpatib pou konfigirasyon.

2. Èske EPF6016ATC144-2N apwopriye a pou ti pwodiksyon kouri oswa prototip?

Wi.Pake TQFP-144 li fè li fasil pwototip san yo pa bezwen an pou zouti asanble avanse.Li la tou ideyal pou ti-echèl pwodiksyon kote ki ba pri ak fleksibilite yo bezwen.

3. Ki jan EPF6016ATC144-2N a konpare ak plus FPGAs an tèm de pèfòmans?

Pandan ke yo pa tankou karakteristik ki rich tankou modèn-wo fen FPGAs, EPF6016ATC144-2N a ofri pèfòmans serye pou konpleksite lojik modere ak pi ba konsomasyon pouvwa ak entegrasyon pi senp, fè li pri-efikas pou anpil aplikasyon.

4. Èske li san danje nan cho-ploge nan EPF6016ATC144-2N nan sistèm ap viv?

Wi.FPGA sa a sipòte cho-kou.

5. Poukisa mwen ta dwe chwazi EPF6016ATC144-2N sou Custom ASIC oswa CPLD solisyon yo?

EPF6016ATC144-2N a ofri sik devlopman pi vit, nan-jaden rprogramasyon, ak redwi pri inicio konpare ak ASICs.Konpare ak CPLDs, li bay plis kapasite lojik ak routage fleksib, ideyal pou desen évolutive ak en.

LC5768MC-75F256C CPLD: karakteristik, karakteristik, avantaj ak aplikasyon pou

sou 2025/07/10

Pou kòmanse ak MC7447AHX1000NB

sou 2025/07/10

Posts popilè

-

Enstriksyon konplèks Set Odinatè: Ki jan yo chanje informatique?

sou 8000/04/19 147782

-

USB-C pinout ak karakteristik

sou 2000/04/19 112064

-

Sèvi ak Xilinx Inifye Simulation Primitif: Yon Gid konplè nan FPGA Design ak Simulation

sou 1600/04/19 111352

-

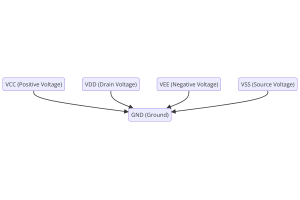

Tansyon ekipman pou pouvwa nan elektwonik: siyifikasyon VCC, VDD, VEE, VSS, ak GND

sou 0400/04/19 83819

-

RJ45 Connector Gid: Pinout, fil elektrik, Kalite Kab, ak Itilizasyon

sou 1970/01/1 79639

-

Gid la ultim nan kòd koulè fil nan sistèm elektrik modèn

Fason sistèm elektrik nou yo itilize koulè yo pa sèlman pou sanble.Chak koulè fil kounye a endike yon fonksyon espesifik, fè li pi fasil yo idantifye ak okipe konpozan elektrik kòrèkteman pandan en...sou 1970/01/1 66999

-

Purge Valv Gid: Fonksyon, sentòm, tès, ak ranplasman pou pèfòmans motè optimal

Valv la weteur se yon pati enpòtan nan sistèm yon machin nan ki ede kenbe lè a pwòp pa jere vapè gaz yo anvan yo ka chape anba nan atmosfè a.Sa a pa sèlman ede anviwònman an pa diminye polisyon, me...sou 1970/01/1 63125

-

Kalite (q) Faktè: Ekwasyon ak aplikasyon

Faktè bon jan kalite a, oswa 'Q', se enpòtan lè tcheke ki jan byen endukteur ak rezonan travay nan sistèm elektwonik ki itilize frekans radyo (RF).'Q' mezire ki jan byen yon sikwi minimize pèt enèj...sou 1970/01/1 63062

-

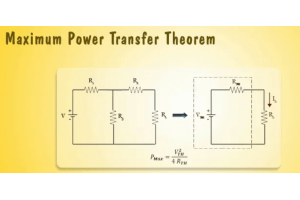

Atenn pèfòmans pik ak teyorèm nan transfè pouvwa maksimòm

Teyorèm maksimòm transfè pouvwa a eksplike kijan enèji ki sòti nan yon sous, tankou yon batri oswa dèlko, ap koule nan yon chaj ki konekte.Li montre kondisyon an egzak kote chaj la resevwa pouvwa k...sou 1970/01/1 54097

-

Espesifikasyon batri A23 ak konpatibilite

Batri a A23 se yon ti, silenn ki gen fòm batri ak vòltaj segondè.Yo te rele tou 23a, 23AE, oswa MN21, li kouri nan 12 vòlt ak pi wo pase AA oswa AAA pil.Konsepsyon espesyal li fè li pafè p...sou 1970/01/1 52215