EPM7192SQC160-15 CPLD: Karakteristik, pinout, pwogramasyon ak aplikasyon pou

Gid sa a pale sou EPM7192SQC160-15 la, yon chip lojik pwogramasyon soti nan fanmi an Max 7000s.Li eksplike ki sa chip la ka fè, ki jan li fonksyone, ak ki kote li ka itilize.Li montre ki jan chip la bati andedan, ki sa chak PIN fè, ak ki jan li konekte nan lòt pati yo.Gid la gen ladan tou kote sa a chip ka itilize, ki jan nan pwogram li etap pa etap, ki sa lòt bato ki sanble egziste, epi ki moun ki fè li.Katalòg

Ki sa ki EPM7192SQC160-15 la?

A EPM7192SQC160-15 se yon CPLD mitan-ranje (konplèks aparèy lojik pwogramasyon) soti nan fanmi MAX 7000S, te fè pou serye kontwòl lojik dijital nan entegre ak sistèm endistriyèl.Chip sa a ofri Macrocells 192 ak sou 3,750 pòtay lojik, bay ase kapasite pou manyen travay lojik modere.Li gen ladan 124 I/O broch, ak kouri sou ekipman pou 5V, ak multivolt I/O sipò nan koòdone ak tou de 3.3V ak 5V sistèm lojik.Nan-sistèm li yo pwogramasyon ki baze sou achitekti ki baze sou vle di ou ka rprograme li dirèkteman nan kous ou lè l sèvi avèk JTAG, san yo pa bezwen eleman siplemantè oswa memwa ekstèn.Avèk yon klas vitès nan –15, li sipòte frekans revèy sistèm jiska sou 76.9 megaèrts, ofri vit ak konsistan pèfòmans distribisyon pou lajè aplikasyon dijital.Se fanmi an Max 7000s li te ye pou pèfòmans solid li yo, memwa EEPROM, ak operasyon vòltaj fleksib.

Kap chèche EPM7192SQC160-15?Kontakte nou yo tcheke stock aktyèl, tan plon, ak prix.

EPM7192SQC160-15 CAD Modèl

EPM7192SQC160-15 senbòl

EPM7192SQC160-15 anprint

EPM7192SQC160-15 3D modèl

EPM7192SQC160-15 karakteristik

192 Macrocells: Aparèy la gen ladan 192 Macrocells, ki sèvi kòm eleman yo nwayo pwogramasyon.Sa yo macrocells ka configuré aplike yon gran varyete konbinezon ak sekans fonksyon lojik ki nesesè nan desen dijital.

Apeprè 3,750 pòtay lojik: Li ofri yon kapasite lojik ekivalan nan alantou 3,750 pòtay, fè li apwopriye pou medyòm-konplèks kontwòl lojik, machin eta a, oswa lojik lakòl nan sistèm entegre.

Nan-sistèm pwogramasyon via JTAG: Li prezante memwa EEPROM ki baze sou ki pèmèt reprogramasyon dirèkteman nan sistèm lan lè l sèvi avèk yon koòdone JTAG estanda, sipòte tou de IEEE 1149.1 ak IEEE 1532 estanda.

Maksimòm frekans jiska 125 megaèrts: Lojik entèn la ka opere nan vitès revèy rive 125 megaèrts, pèmèt pwosesis vit pou aplikasyon pou distribisyon-sansib.

Pwopagasyon reta nan 7.5 ns: Chip la ofri yon reta pwopagasyon ki ba nan apeprè 7.5 nanoseconds, asire rapid repons siyal soti nan opinyon nan pwodiksyon.

Sipòte 5V ekipman pou ak multivolt I/O: Aparèy la kouri sou yon ekipman pou nwayo 5V ak sipòte multivolt I/O, sa ki pèmèt konpatibilite ak tou de 5V ak 3.3V nivo siyal pou entegrasyon fasil nan melanje-vòltaj sistèm yo.

Pousantaj pwogramasyon ak rezilta louvri-drenaj: Ou ka kontwole pousantaj kwen siyal pou rediksyon EMI epi chwazi rezilta louvri-drenaj pou branche-yo ak lojik oswa nivo chanjman.

Sis pwodiksyon mondyal pèmèt siyal: Sa yo siyal kontwòl mondyal pèmèt pèmèt oswa enfimite rezilta nan tout miltip I/O bank pou jesyon siyal efikas.

Configurable baskile-flops nan macrocells: Chak MacroCell gen ladan yon baskile-flop ki sipòte prereglaj, klè, revèy pèmèt, ak kontwòl endividyèl, bay ranfòse fleksibilite pou konsepsyon lojik sekans.

Mode ba-pouvwa: Aparèy la gen ladan yon karakteristik ekonomize pouvwa ki ka koupe konsomasyon pouvwa Macrocell pa plis pase 50%, ki se benefis pou aplikasyon pou enèji-efikas.

Sipò tès JTAG fwontyè-eskanè : Aparèy ak 128 oswa plis macrocells, tankou sa a yon sèl, gen ladan yo plen limit-eskanè tès karakteristik pou efikas tablo-nivo diagnostics ak validation.

Ti jan sekirite pou pwoteksyon konsepsyon: Yon ti jan sekirite pwogramasyon asire ke konsepsyon entèn la pa ka li oswa kopye, pwoteje pwopriyete entelektyèl.

PCI-konpatib mwen/O: Se estrikti a I/O ki fèt satisfè psi kondisyon elektrik, pèmèt interfacing dirèk ak sistèm psi ki baze sou.

Operasyon tanperati ranje 0 ° C a 70 ° C: Ranje estanda tanperati komèsyal-klas la fè aparèy sa a apwopriye pou pifò aplikasyon andedan kay la ak kontwole-anviwònman an.

EPM7192SQC160-15 Pinout Dyagram

Dyagram sa a montre Layout PIN la pou EPM7192SQC160-15 ak menm aparèy Max 7000s.Chip la gen 160 broch ranje alantou tout kat kote nan yon pake kare QFP.PIN 1 kòmanse nan kwen an tèt-gòch ak nimewo ale envers alantou chip la.Chak bò gen 40 broch.Ti pwen an nan tèt-gòch mak PIN 1, ki ede ak plasman apwopriye.Non an chip nan sant la montre li nan konpatib ak lòt modèl nan menm fanmi an.Layout sa a bay anpil koneksyon I/O epi li itil pou desen lojik konplèks.

Max 7000s blòk dyagram

Dyagram sa a blòk montre estrikti entèn nan MAX 7000S CPLD a, ki gen ladan EPM7192SQC160-15 la.Se chip la divize an kat seksyon prensipal yo rele blòk etalaj lojik (laboratwa A a D).Chak laboratwa gen 16 macrocells, ki se ti inite lojik itilize yo bati sikwi dijital.Ansanm, sa yo laboratwa okipe operasyon lojik konplèks.

Nan sant la se etalaj la konekte pwogramasyon (PIA), ki konekte tout laboratwa ak pèmèt yo pataje done.Chak laboratwa voye ak resevwa siyal nan 36 chanèl, bay fleksib routage ant blòk lojik.Anviwon bor yo, gen I/O blòk kontwòl ki lyen 6 a 16 I/O broch nan chak laboratwa, sa ki pèmèt aparèy la konekte ak lòt pati nan yon sistèm.

Nan tèt la, siyal kontwòl mondyal tankou revèy ak pwodiksyon pèmèt yo montre.Siyal sa yo ede jere ki jan done deplase andedan chip a ak lè rezilta yo aktif.An jeneral, dyagram lan montre kouman EPM7192SQC160-15 òganize lojik li yo ak koneksyon pou sipòte desen dijital koutim.

EPM7192SQC160-15 Espesifikasyon

|

Lèt |

Paramèt |

|

Fabrikan |

Altera |

|

Seri |

Max® 7000s |

|

Anbalaj |

Plato |

|

Estati pati |

Demode |

|

Kalite pwogramasyon |

Nan sistèm pwogramasyon |

|

Reta tan TPD (1) Max |

15 ns |

|

Pwovizyon pou vòltaj - Entèn |

4.75V ~ 5.25V |

|

Kantite eleman lojik/blòk |

12 |

|

Kantite macrocells |

192 |

|

Kantite pòtay |

3750 |

|

Kantite I/O |

124 |

|

Tanperati opere |

0 ° C ~ 70 ° C (TA) |

|

Kalite aliye |

Sifas mòn |

|

Pake / Ka |

160-BQFP |

|

Pake aparèy founisè |

160-PQFP (28x28) |

|

Nimewo pwodwi baz |

EPM7192 |

EPM7192SQC160-15 Aplikasyon

Embedded System lakòl lojik

EPM7192SQC160-15 la se ideyal pou pase diferan aparèy dijital nan sistèm entegre.Li kapab itilize nan jere kominikasyon ant mikrokontroleur, bato memwa, ak I/O aparèy pa manyen adrès dekodaj, kontwòl otobis, ak ajisteman distribisyon san yo pa bezwen lojik disrè ICS.

Machin eta ak lojik kontwòl

Avèk Macrocells 192 li yo, chip a se byen adapte pou mete ann aplikasyon machin eta koutim ak lojik kontwòl.Li nan souvan itilize nan travay automatisation, contrôleur motè, ak distribisyon ki baze sou sistèm kontwòl ki mande pou serye ak repete tranzisyon eta a.

Kominikasyon pwotokòl interfaces

Sa a CPLD ka pwograme yo kreye oswa tradwi pwotokòl kominikasyon tankou UART, SPI, I²C, oswa koutim fòma seri.Li pèmèt konfigirasyon fasil ak modifikasyon san yo pa chanje pyès ki nan konpitè, fè li valab pou entèfas kominikasyon.

Siyal dijital pre-pwosesis

Mèsi a vitès lojik vit li yo ak reta ki ba pwopagasyon, li ka okipe travay senp pwosesis siyal tankou filtraj, multiplexing, oswa deteksyon kwen anvan siyal rive nan processeur prensipal la oswa chip DSP.

Tradiksyon koòdone ak nivo déplacement

Kapasite I/O li yo sipòte tou de siyal 3.3V ak 5V.Sa fè li apwopriye pou desen ki gen ladan konpozan opere nan nivo vòltaj diferan, sa ki pèmèt tradiksyon vòltaj san danje epi efikas.

Rapid Prototype ak In-System Updates

Ou ka itilize chip sa a nan sistèm ki ka mande pou dènye lojik souvan.Estrikti EEPROM ki baze sou li yo ak koòdone pwogram JTAG fè li posib rprograme lojik la menm apre yo fin tablo a reyini.

Tès tablo-nivo ak diagnostics

Avèk sipò fwontyè-eskanè via JTAG, li teste koneksyon ki genyen ant bato sou yon PCB san yo pa bezwen sond.Sa a se itil pandan manifakti ak nan-jaden diagnostics pou detekte soudaj oswa pwoblèm routage.

EPM7192SQC160-15 Pati ki sanble

• EPM7192EQC160-20 (Altera)

Aparèy sa a se soti nan menm Max 7000 seri a epi li ofri menm resous yo lojik, 192 MacroCells ak 124 I/O broch nan yon pake 160-PIN PQFP.Li opere nan yon klas vitès pi dousman nan -20, sa vle di li gen pi long reta pwopagasyon (~ 20 ns), men li toujou satisfè bezwen yo nan ki pa tan-kritik desen.Li se yon altènatif apwopriye pou aplikasyon pou kote dansite lojik enpòtan, men ultra-vit distribisyon se pa yon priyorite, fè li ideyal pou pwojè pri-sansib ki toujou bezwen ekivalans fonksyonèl.

• EPM7192SQI160-10N (Altera)

Pati sa a se tou lojik-konpatib ak EPM7192SQC160-15 la, ofri menm kantite macrocells ak mwen/os.Sepandan, li sèvi ak yon klas vitès –10, ki sipòte operasyon pi vit ak distribisyon amelyore (10 ns reta pwopagasyon).Li sipòte tou yon ranje tanperati pwolonje soti nan -40 ° C a +85 ° C, fè li yon ranplasan ekselan pou aplikasyon pou endistriyèl oswa deyò.Sa fè li ideyal lè pi wo vitès ak detèminasyon anviwònman yo gen obligasyon.

• EPM7192SQC160-7 (Intel)

Kòm yon Variant dirèk vitès-up nan EPM7192SQC160-15 la, vèsyon an –7 delivre pèfòmans ki pi rapid nan fanmi an, ak reta pwopagasyon desann nan 7.5 ns.Li kenbe menm konfigirasyon PIN la, karakteristik pouvwa, ak dansite lojik, ofri yon ranplasman gout-an pou moun k ap chèche pi bon vitès san yo pa chanje Layout tablo oswa kondisyon vòltaj.Sa fè li pi bon chwa pou desen distribisyon-kritik ki bezwen pi vit repons siyal pandan y ap rete nan anprint nan menm konsepsyon.

EPM7192SQC160-15 etap pwogramasyon

1. Antre mòd ISP

Premye etap la se chanjman aparèy la nan ISP (nan-sistèm pwogramasyon) mòd.Sa a se fè nan koòdone nan JTAG.Yon fwa nan mòd ISP, tout I/O broch yo sou aparèy la yo mete nan yon mòd ki an sekirite tri-eta yo anpeche entèferans lojik entansyonel pandan pwogramasyon.Sa a inisyalizasyon tipikman pran apeprè 1 milisgond.

2. Tcheke ID aparèy la

Yon ID inik Silisyòm entegre nan aparèy la pou verifye li se modèl ki kòrèk la anvan pwogramasyon an kòmanse.Sistèm nan orè nan yon enstriksyon li ak rekupere ID a atravè TDO a (done tès soti) liy lan.Chèk sa a asire ke se zouti nan pwogramasyon ki konekte nan CPLD a dwa ak evite erè tankou ranplasan yon pati diferan.

3. Efase esansyèl

Yon efase esansyèl efase tout done ki te deja estoke nan memwa EEPROM nan CPLD la.Sa a prepare chip a pou resevwa yon nouvo konfigirasyon.Kòmandman an efase inisye yon batman kè ki tipikman dire alantou 100 milisgond, asire tout selil pwogramasyon yo Reyajiste.

4. Pwogram EEPROM

Se done konfigirasyon nouvo chaje nan aparèy la pa chanje adrès ak Bits done nan pò a JTAG.Chak selil memwa ekri youn pa youn, ak yon batman kè pwogramasyon aplike apre chak sik ekri siksè.Pwosesis sa a defini estrikti lojik CPLD a pral itilize lè mache.

5. Verifye eeprom

Apre pwogramasyon an, aparèy la fè yon etap verifikasyon.Sa a enplike nan lekti tounen chak kote memwa pwograme ak konpare valè yo pwodiksyon kont done yo gen entansyon.Si verifikasyon an echwe, pwosesis la dwe repete.Etap sa a garanti konfigirasyon an te ekri avèk siksè.

6. Sòti mòd ISP

Yon fwa verifikasyon an konplè, se yon lòd final bay sòti mòd ISP.Aparèy la reyaktif I/O broch li yo ak rezime operasyon nòmal.Tranzisyon sa a tou pran apeprè 1 milisgond epi konplete sik nan pwogram nan sistèm lan.

EPM7192SQC160-15 dimansyon anbalaj

• Gwosè kò: 28mm × 28mm

• Wotè pake: 3.4mm

• Anplasman PIN: 0.65mm

EPM7192SQC160-15 manifakti

EPM7192SQC160-15 la te orijinèlman manifaktire pa Altera Corporation, yon konpayi li te ye pou avanse aparèy lojik pwogramasyon li yo.Nan 2015, Altera te rann pa Intel Corporation, ak aparèy la se kounye a yon pati nan gwoup solisyon pwogramasyon Intel a anba Max 7000s fanmi an CPLD.Intel kontinye sipòte pwodwi Legacy Altera, byenke EPM7192SQC160-15 la kounye a klase kòm demode nan pi katalòg ofisyèl yo.Malgre estati sispann li yo, repitasyon istorik Intel a pou fyab ak eritaj Altera a nan solisyon lojik pèfòmans-wo asire kontinye demann ak disponiblite nan distribitè segondè.

Konklizyon

EPM7192SQC160-15 la se yon chip itil ak fleksib pou manyen travay kontwòl dijital nan anpil sistèm elektwonik.Li ofri ase pouvwa lojik pou travay tankou bati machin eta koutim, manyen siyal, ak konekte aparèy diferan.Li sipòte diferan nivo vòltaj, travay nan vitès vit, epi yo ka mete ajou fasil nan JTAG.Konsepsyon entèn li yo pèmèt koule siyal lis ak chanjman lojik fasil.Menm si li se kounye a sispann, li la toujou yon gwo opsyon pou pwojè fin vye granmoun oswa kontinyèl, epi yo ka ranplase ak bato ki sanble ki ofri pi vit oswa pi laj sipò tanperati.

Fich pdf

EPM7192SQC160-15 fich:

Sou nou

ALLELCO LIMITED

Li piplis

Quick Inquiry

Tanpri voye yon ankèt, nou pral reponn imedyatman.

Kesyon yo poze souvan [FAQ]

1. Èske mwen ka pwogram EPM7192SQC160-15 la san yo pa retire li nan tablo a sikwi?

Wi, chip la sipòte nan-sistèm pwogramasyon (ISP) atravè koòdone nan JTAG, kidonk, ou ka pwogram oswa rprograme li dirèkteman pandan ke li se soude sou PCB a, ki senplifye dènye konsepsyon ak diminye rivork.

2. Ki lojisyèl pwogramasyon mwen ta dwe itilize pou EPM7192SQC160-15?

Ou ka itilize Altera a Quartus II lojisyèl (ki pi gran vèsyon) yo kreye desen lojik, konpile kòd la, ak jere pwosesis la pwogramasyon ki baze sou JTAG.Quartus II sipòte Max 7000s aparèy tankou EPM7192SQC160-15 la.

3. Èske EPM7192SQC160-15 a mande pou memwa ekstèn pou operasyon?

Non, li gen memwa konfigirasyon entèn ki baze sou EEPROM.Se tout konfigirasyon lojik ki estoke andedan chip a, kidonk pa gen okenn memwa ekstèn ki nesesè pou estoke eta lojik oswa sekans bòt.

4. Ki sa ki fè EPM7192SQC160-15 apwopriye a pou itilize endistriyèl?

Operasyon gaya 5V li yo, multivolt I/O konpatibilite, pwosesis lojik vit, ak EEPROM ki baze sou memwa ki pa temèt fè li serye pou sistèm endistriyèl ki mande pou ki estab ak dirab fonksyon lojik dijital.

5. Kijan EPM7192SQC160-15 manch sistèm vòltaj melanje?

Mèsi a sipò multivolt I/O li yo, aparèy la ka koòdone ak tou de 3.3V ak 5V nivo lojik, fè li ideyal pou melanje-siyal sistèm ak entèfas ak modèn ki ba-vòltaj konpozan.

Poukisa chwazi EPF10K100EFC484-3 pou pwojè ou a

sou 2025/06/13

Ki sa ki se yon switch SPST ak ki jan li travay?

sou 2025/06/12

Posts popilè

-

Enstriksyon konplèks Set Odinatè: Ki jan yo chanje informatique?

sou 8000/04/18 147766

-

USB-C pinout ak karakteristik

sou 2000/04/18 111994

-

Sèvi ak Xilinx Inifye Simulation Primitif: Yon Gid konplè nan FPGA Design ak Simulation

sou 1600/04/18 111351

-

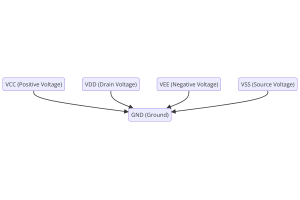

Tansyon ekipman pou pouvwa nan elektwonik: siyifikasyon VCC, VDD, VEE, VSS, ak GND

sou 0400/04/18 83756

-

RJ45 Connector Gid: Pinout, fil elektrik, Kalite Kab, ak Itilizasyon

sou 1970/01/1 79550

-

Gid la ultim nan kòd koulè fil nan sistèm elektrik modèn

Fason sistèm elektrik nou yo itilize koulè yo pa sèlman pou sanble.Chak koulè fil kounye a endike yon fonksyon espesifik, fè li pi fasil yo idantifye ak okipe konpozan elektrik kòrèkteman pandan en...sou 1970/01/1 66951

-

Purge Valv Gid: Fonksyon, sentòm, tès, ak ranplasman pou pèfòmans motè optimal

Valv la weteur se yon pati enpòtan nan sistèm yon machin nan ki ede kenbe lè a pwòp pa jere vapè gaz yo anvan yo ka chape anba nan atmosfè a.Sa a pa sèlman ede anviwònman an pa diminye polisyon, me...sou 1970/01/1 63094

-

Kalite (q) Faktè: Ekwasyon ak aplikasyon

Faktè bon jan kalite a, oswa 'Q', se enpòtan lè tcheke ki jan byen endukteur ak rezonan travay nan sistèm elektwonik ki itilize frekans radyo (RF).'Q' mezire ki jan byen yon sikwi minimize pèt enèj...sou 1970/01/1 63028

-

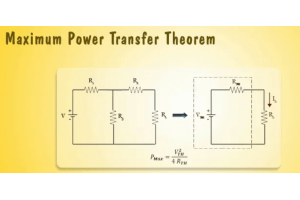

Atenn pèfòmans pik ak teyorèm nan transfè pouvwa maksimòm

Teyorèm maksimòm transfè pouvwa a eksplike kijan enèji ki sòti nan yon sous, tankou yon batri oswa dèlko, ap koule nan yon chaj ki konekte.Li montre kondisyon an egzak kote chaj la resevwa pouvwa k...sou 1970/01/1 54094

-

Espesifikasyon batri A23 ak konpatibilite

Batri a A23 se yon ti, silenn ki gen fòm batri ak vòltaj segondè.Yo te rele tou 23a, 23AE, oswa MN21, li kouri nan 12 vòlt ak pi wo pase AA oswa AAA pil.Konsepsyon espesyal li fè li pafè p...sou 1970/01/1 52176