Field-Pwogramasyon Gate Array (FPGA): Pwogrè, Achitèk, ak aplikasyon nan modèn Elektwonik

Gid sa a eksplore teknoloji a FPGA (jaden-pwogramasyon pòtay), inovasyon kondwi tan kap vini an nan konsepsyon sikwi dijital.Kontrèman ak bato fiks-fonksyon, FPGAs ka reprogramasyon pou adapte yo ak bezwen chanje.Atik la kouvri wòl enpòtan yo nan endistri tankou telekominikasyon ak dijital pwosesis siyal, ofri Sur nan achitekti yo, aplikasyon pou yo, ak ap grandi enpak sou elektwonik modèn.Katalòg

Pwogrè nan teknoloji FPGA

Teknoloji jaden-pwogramasyon pòtay (FPGA) teknoloji vle di soti pou adaptabilite li yo, ofri solisyon reprogrammable pyès ki nan konpitè ki ka Customized pou aplikasyon pou diferan, kontrèman ak bato fiks-fonksyon tankou ASICS.Fleksibilite sa a te fè FPGAs enpòtan nan jaden tankou sistèm kominikasyon, pwosesis siyal dijital, ak aprantisaj machin.Peyi tankou China ap jwe yon wòl nan avanse Inovasyon FPGA pa devlope solisyon sofistike ki amelyore kanpe teknolojik yo.Kòm FPGAS evolye, yo ale wout la pou kolaborasyon kwa-fontyè ak inovasyon, ede endistri adrese defi modèn ak Customized, pyès ki nan konpitè pèfòmans-wo.Kontrèman ak metòd informatique tradisyonèl yo, ki konte sou pwosesis sekans, FPGAS ogmante pwosesis paralèl okipe travay konplèks pi plis efikasite.Anpil sèvi ak pyès ki nan konpitè deskripsyon lang (HDLs) nan pwogram sa yo bato, sa ki pèmèt yo nan konsepsyon algoritm konplike dirèkteman nan pyès ki nan konpitè pou pèfòmans pi vit.Metrize devlopman FPGA mande pou yon balans nan konesans teyorik ak men-sou eksperyans nan pyès ki nan konpitè-lojisyèl entegrasyon.Apwòch sa a inik nan kalkil bay FPGAs yon kwen nan zòn tankou chifreman, AI, ak pwosesis done yo, ki fè yo zouti gwo pou pwogrè nan lavni teknolojik nan tout endistri yo.

Vwayaj la nan teknoloji FPGA

Lè Xilinx entwodwi FPGA XC2064 an 1985, li te deklanche yon transfòmasyon nan teknoloji, chanje peyizaj la pandan yon tan jis kòmanse anbrase òdinatè pèsonèl, entènèt la, ak telefòn mobil yo.Innovations sa yo te pwovoke yon nouvo epòk ki santre sou entegrasyon dijital.Okòmansman fè travay lojik debaz, FPGAs rapidman pwogrese, jwenn valè nan pwosesis dijital ak aplikasyon pou entegre.Avèk de deseni nan devlopman inplakabl, FPGAs evolye nan pati oksilyè nan pouvwa pwòp tèt ou-otè, reflete evolisyon an rapid nan endistri a semi-conducteurs.Their journey showcases a striking leap in complexity, advancing from an early 2μm process with 85,000 transistors to advanced billion-transistor devices using technologies like 65nm by 2007. A moment occurred in 1991 when Xilinx's XC4000 series emerged, which fostered a broad embrace of programmable logicAtravè kreyasyon ak pwosesis evalyasyon nan endistri an.Sa a kwasans teknolojik kontinyèl alimenté endistri a FPGA, satisfè demann lan ogmante pou konplike solisyon semi -conducteurs.Kapasite FPGAs 'efor entegre ak fè pou sèvi ak nouvo teknoloji sèvi kòm yon testaman siyifikasyon nan adaptabilite ak previzyon nan jeni.Pa san pran souf amelyore ak elaji fonksyonalite yo, FPGAs pa sèlman kenbe okouran de avans teknolojik men souvan enfliyanse trajectoire nan lavni li yo.

Prensip nan fonctionnalités FPGA

Estrikti FPGA ak konpozan

Field pwogramasyon pòtay ranje (FPGAs) itilize yon achitekti konplèks li te ye tankou etalaj la selil lojik (LCA).Kad sa a enkòpore blòk lojik configurable (CLBs), blòk pwodiksyon opinyon (IOBs), ak yon rezo vaste nan konèksyon.Tankou yon achitekti ponn baz la pou desen lojik trè reglabl.Kontrèman ak tradisyonèl sikwi lojik fiks, FPGA fè grandizè kapasite a remakab nan rkonfigurasyon.Pandan ke sikwi estatik rete chanje, FPGA transfòme operasyon lojik nan loading a egzak nan done configurable nan selil RAM estatik, amelyore adaptabilite yo.Sa a trè entansifye valè yo kòm tou de konpozan kenkayri dinamik ak tribin pou aplikasyon pou pyonye atravè jaden divès.

Adapte pwosedi lojik

Ankadreman an laj ak reprogramabl nan FPGA ranfòse pou aplike pou divès kalite transfòmasyon lojik repete.Pa ak anpil atansyon loading done konfigirasyon espesifik nan eleman memwa yo, moun ki ka Customize travay lojik ak presizyon eksepsyonèl.Sa yo personnalisation sipòte yon etalaj lajè de bezwen pwojè ak mete aksan sou depa FPGAs yo soti nan predesesè fiks yo tankou pal ak cplds, fasilite prèske san limit opòtinite reprogramasyon lojik.Sa a adaptabilite pwouve anpil valè nan endistri ki nesesè chanjman souvan, tankou telekominikasyon ak pwosesis siyal.

Divès entegrasyon aplikasyon an

FPGAS fonksyone kòm yon pon efikas ant aparèy lojik fiks ak aplikasyon-espesifik sikwi entegre (ASICs), ofri adaptabilite san yo pa transfere depans sa yo apik nan kenkayri koutim.Fleksibilite yo fè pwomosyon l 'nan aplikasyon pou divès kalite, ki gen ladan sistèm komès-wo frekans ak teknoloji avyon.Bon jan kalite sa a se avantaje pandan premye etap pwototip, kote amelyorasyon iteratif ka rive san yo pa nesesite refè pyès ki nan konpitè konplè.Nan anviwònman konplike, kapasite a nan FPGAs an menm tan jere travay miltip egzanpifye entre la Harmony ant kenkayri reponn ak demand yo dinamik nan lojisyèl modèn.Reflete sou achitekti a ak potansyèl de FPGA revele ke fòs vre yo se nan anpil fleksibilite yo.Sa a atribi revolusyone endistri rezoud pwoblèm apwòch, sa ki pèmèt pou solisyon ki pwogrè ansanm ak pwogrè teknolojik.Insights nan endistri a endike ke reconfigurability nan nannan nan FPGAs fè yo yon eleman pou aplikasyon pou pi devan-kap, kote distenksyon ki genyen ant lojisyèl ak pyès ki nan konpitè vin de pli zan pli indistinct.

Estrikti debaz nan aparèy FPGA

Aparèy FPGA fè pati nan kategori a nan sikwi semi-koutim nan sikwi espesyalize entegre, fabrike yo ofri fleksibilite ak yon gwo ranje nan fonksyon.Yo enkòpore anpil resous tankou inite pwogramasyon/pwodiksyon pwogramasyon, blòk lojik configurable, ak modil pou jesyon revèy dijital.Konpozan sa yo kreye yon fondasyon dinamik, sa ki pèmèt pwogramasyon remakab, ki ede adrese defi yo fè fas a pa aparèy ak konte pòtay limite.Resous yo konekte anpil entegre nan FPGAs fasilite wo-entegrasyon ak desen serye, ki egzije relativman modere envestisman inisyal la.Sa a trè fè FPGAs atiran nan sikwi yo dijital.

Vwayaj la nan konsepsyon FPGAs jeneralman suiv yon metòd òganize.Pou kòmanse, se achitekti a algorithm fabrike, sèvi kòm yon plan estratejik pou etap ki vin apre.Apre sa, simulation sistèm pran plas, bay ak Sur nan pwoblèm potansyèl anvan tranzisyon nan aplikasyon fizik.Etap final la enplike nan validasyon sou pyès ki nan konpitè nan prototip repete, asire ke nenpòt ajisteman yo tou de pratik ak efikas.Sa a se sik devlopman arichi anrichi pa pwosesis divès itilize elektwonik konsepsyon automatisation (EDA) zouti.Zouti sa yo kontribye nan raffinage ak optimize konsepsyon an aliman ak kondisyon pratik.

Yon eleman enpòtan nan pwosesis devlopman sa a se nati siklik kreyasyon ak tès la.Yon fwa desen teyorik yo fini ak amann-branche nan similasyon, kontrent yo nouvo yo egzekite ak valide sou aktyèl pyès ki nan konpitè FPGA.Sa a entre kontinyèl ant konsepsyon ak tès fizik asire ke rezilta a se tou de gaya ak efikas.Yon pèspektiv sezonman apresye enpòtans ki genyen nan sik sa yo repete, rekonèt ekilib ki genyen ant ideyal konseptyèl ekspresyon ak limit pratik, finalman ki mennen ale nan desen FPGA siksè.Akimilasyon nan inisyativ sa yo pwodui yon detaye, adaptab, ak konfyans sistèm FPGA, ekipe yo atake complexités yo nan sikwi dijital.

Prensip k ap travay pou FPGA Chip Design

Designing bato FPGA mande pou yon fondasyon ki byen estriktire ak yon apwòch metodik ki aliyen ak demand yo espesifik nan achitekti FPGA.Pwosesis la enplike nan tradui algoritm konplèks nan desen pratik lè l sèvi avèk zouti avanse tankou MATLAB oswa C. pa aplike pyès ki nan konpitè deskripsyon lang (HDLs) ak presizyon, ou ka asire klè, fonctionnalités, ak entegrasyon efikas nan eleman nan fondasyon an FPGA.Aspè nan konsepsyon FPGA se entegrasyon an san pwoblèm nan konpozan pyès ki nan konpitè ak atansyon a chema.Anpil tankou ki jan achitèk konte sou plan detaye, FPGA konsèpteur konsantre sou konekte kouch nan pòtay lojik ak interfaces reyalize pèfòmans nan vle.Kowòdinasyon sa a atravè tout eleman konsepsyon asire ke pwodwi final la opere avèk efikasite ak satisfè kondisyon fonksyonèl.

Devlopman algorithm ak tradiksyon yo se etap kle nan konsepsyon FPGA.Anpil kreye algoritm konplike nan wo nivo lang yo ak rafine yo iterativman asire yo tradui avèk presizyon nan FPGA-konpatib achitekti.Pwosesis la miwa sik devlopman lojisyèl, kote tès kontinyèl ak amelyorasyon mennen nan pi bon pèfòmans.Metriz nan HDLS plis amelyore pwosesis sa a pa fè kòd la pi lizib, efikas, ak pi fasil debug.Verifikasyon ak debogaj nan nivo tablo yo bezwen asire ke konsepsyon final la se serye ak satisfè atant itilizatè.Etap sa a enplike nan tès apwofondi, menm jan ak yon lis pre-vòl, trape nenpòt pwoblèm potansyèl anvan deplwaman.Pratik verifikasyon solid diminye risk ak amelyore fyab la an jeneral nan chip la FPGA, asire fonksyonalite alontèm ak tan pi vit nan mache.

Lang konsepsyon ak tribin

Pwogrè nan pratik konsepsyon FPGA

Field-programmable ranje pòtay (FPGAs) yo trè versatile aparèy kenkayri ki ka Customized fè travay espesifik.Pou desine fonksyon sa yo Customized, anpil konte sou pyès ki nan konpitè deskripsyon lang (HDLs), ki pèmèt yo defini ki jan yon sistèm dijital ta dwe konpòte yo.De nan HDL yo pi souvan itilize nan konsepsyon FPGA yo se VHDL ak Verilog HDL.Lang sa yo sèvi kòm fondasyon pou kreye konplèks sikwi dijital pa bay yon fason yo modèl konpòtman sistèm lan anvan li se fizikman aplike.Kapasite sa a dekri konpòtman pyès ki nan konpitè nan kòd ede optimize pèfòmans sistèm ak reyalize fonksyonalite egzak.

VHDL, ki vle di pou VHSIC pyès ki nan konpitè deskripsyon lang, se yon lang lajman adopte nan konsepsyon FPGA paske nan anfaz li yo sou Transparans ak endepandans konsepsyon.Li pèmèt yo ekri kòd ki ka adapte a achitekti pyès ki nan konpitè diferan, fè li pi fasil pou itilize ankò desen atravè pwojè miltip.VHDL se itil pou pwojè ki mande pou yon wo nivo de kontwòl sou achitekti sistèm, kòm li pèmèt yo bati solisyon trè Customized pwepare a aplikasyon espesifik.Nan lòt men an, Verilog se souvan pi pito pou pi senp li yo, C-tankou sentaks, ki fè li pi aksesib ki abitye avèk lang pwogramasyon tradisyonèl yo.Verilog se popilè pou gwo-echèl, pwosesis konsepsyon milti-etap kote klè ak fasilite nan itilize yo bezwen.

Tou de VHDL ak Verilog kontinye evolye, entwodwi karakteristik plis avanse ki fè workflows konsepsyon FPGA pi efikas.Lang sa yo kounye a sipòte plis sofistike konstwi lojik, ki rasyonalize pwosesis la konsepsyon ak amelyore pwodiktivite.Nati a repete nan konsepsyon FPGA ankouraje aprantisaj kontinyèl ak amelyorasyon, sa ki pèmèt pouse limit yo nan sa ki aparèy sa yo adaptab ka reyalize nan endistri divès kalite.

Anviwònman devlopman entegre (IDES)

Anplis de sa nan pyès ki nan konpitè deskripsyon lang, FPGA Design mande pou zouti lojisyèl espesyalize li te ye tankou anviwònman devlopman entegre (IDEs) nan jere tout pwosesis la konsepsyon.IDES bay yon seri konplè nan zouti ki ede ekri, tès, ak debug desen FPGA.De nan IDE yo ki pi lajman itilize nan devlopman FPGA yo Quartus II, devlope pa Intel, ak Vivado, devlope pa Xilinx.Sa yo tribin rasyonalize pwosesis la devlopman pa entegre travay konsepsyon divès nan yon koòdone sèl, fè li pi fasil jere pwojè konplèks soti nan kòmanse fini.

Youn nan fonksyon prensipal yo nan IDE sa yo se ede ekri ak òganize kòd avèk efikasite.Anplis de koreksyon kòd debaz, tribin sa yo tou bay zouti simulation ki pèmèt yo teste desen yo nòmalman anvan mete ann aplikasyon yo nan pyès ki nan konpitè.Sa a se yon etap kritik nan pwosesis la konsepsyon paske li ede idantifye ak ranje pwoblèm potansyèl bonè, diminye risk pou yo erè koute chè pandan faz nan aplikasyon fizik.IDE yo ofri tou zouti debogaj ki pèmèt yo analize ki jan sistèm dijital yo ap konpòte yo anba kondisyon diferan, asire ke konsepsyon final la fè jan yo espere a.

Kapasite nan byen vit repete sou desen ak tès konfigirasyon miltip se yon gwo avantaj nan lè l sèvi avèk IDEs.Ou ka fè ajisteman nan desen ki baze sou fidbak soti nan similasyon ak sesyon debogaj optimize pèfòmans ak disponiblite.Pwosesis sa a repete ekonomize tan pa minimize bezwen an pou prototip fizik ak diminye sik la devlopman an jeneral.Lè l sèvi avèk IDEs, ou ka asire ke desen yo final satisfè tout kondisyon teknik ak kontrent pratik, sa ki lakòz plis gaya ak efikas sistèm elektwonik.Kòm aplikasyon pou FPGA kontinye elaji nan zòn tankou IoT, AI, ak Computing Edge, anviwònman devlopman sa yo pral jwe yon wòl de pli zan pli enpòtan nan akselere inovasyon.

Aplikasyon nan FPGAs

Sistèm avanse pwosesis videyo

FPGA kontribye nan evolisyon nan sistèm pwosesis videyo.Pa exploiter vitès yo ak fleksibilite, sistèm sa yo amelyore teknoloji videyo tankou segmentation pou modèn milti-ekran montre.Yo satisfè demann lan ap grandi pou bon jan kalite videyo eksepsyonèl nan pipelined ak paralèl pwosesis done.FPGAs avèk efikasite jere doneflows pa prezante kouran videyo ki satisfè kondisyon pwosesis diferan, enkòpore operasyon li/ekri ki te sipòte pa RAM entegre ak konfigirasyon FIFO nan achitekti sistèm konplèks.Evolisyon rapid la obsève nan jaden sa a benefisye de esè tès kontinyèl ak gwo nivo en tipik nan anviwònman ekspozisyon dinamik.

Sistèm jesyon done efikas

Nan done reta ak konsepsyon depo, FPGA fè wòl, espesyalman nan liy reta pwogramasyon yo itilize nan anviwònman kominikasyon.Atravè memwa ak vann san preskripsyon estrateji, patrone pa RAM oswa FIFO yo, yo optimize efikasite sistèm, transparans akomode chanjman ki fèt nan pwotokòl koneksyon done.Efikasite sa a miyò diminye depans sistemik sou tèt li nan rezo elektwonik.FPGAS egzèsis kontwòl dirèk sou operasyon kat SD, aliyen solisyon jesyon done ak jaden flè nan tout tan-chanje nan defi algorithmic.

Innovations sektè telekominikasyon yo

FPGA sèvi evidans nan telekominikasyon yo, manyen pwotokòl konplike nan estasyon baz yo ak asire operasyon san pwoblèm nan mitan adaptasyon pwotokòl kontinyèl.Agility yo konplete bezwen yo ekonomik ak fonksyonèl nan zòn ki gen anpil moun ki gen aparèy tèminal.Malgre ke okòmansman te favorize nan anfans nan sistèm kominikasyon, FPGA grasyeuz tranzisyon nan sipòte ASICS kòm sistèm sa yo ki gen matirite, aktivman ede rezo pandan faz nan kwasans ak chanjman operasyonèl.Sa a adaptabilite se evidan nan pwojè pilòt ki fèt ranfòse rezo fyab ak debi.

Aplikasyon pou endistriyèl lajè

Beyond telekominikasyon, FPGAs jwenn itilizasyon nan sektè sekirite, endistriyèl, militè, ak avyon.Adaptabilite yo kostim pwotokòl orè nan sistèm sekirite, pandan y ap kontra enfòmèl ant FPGAs adrese nuans bezwen endistriyèl ak solisyon pwepare.Fèmen yo jwe yon wòl nan aplikasyon pou defans.Kòm Arenas teknolojik tankou 5G ak AI elaji, FPGA yo ap tann yo déblotché anpil avni endistriyèl.Etid pilòt nan disiplin sa yo endike pwogrè prometteur nan efikasite ak inovasyon, siyal yon lavni moun rich ak aplikasyon pou divès.

Sou nou

ALLELCO LIMITED

Li piplis

Quick Inquiry

Tanpri voye yon ankèt, nou pral reponn imedyatman.

IRF630 N-Chèn Power MOSFET: Karakteristik, pinout, ak fich

sou 2025/01/13

Field-pwogramasyon Chips Sistèm (FPSCs): Teknoloji, Achitèk, ak Design Toolkit

sou 2025/01/12

Posts popilè

-

Enstriksyon konplèks Set Odinatè: Ki jan yo chanje informatique?

sou 8000/04/18 147764

-

USB-C pinout ak karakteristik

sou 2000/04/18 111984

-

Sèvi ak Xilinx Inifye Simulation Primitif: Yon Gid konplè nan FPGA Design ak Simulation

sou 1600/04/18 111351

-

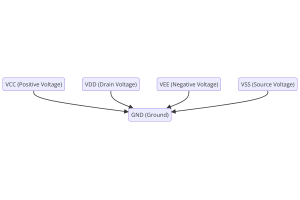

Tansyon ekipman pou pouvwa nan elektwonik: siyifikasyon VCC, VDD, VEE, VSS, ak GND

sou 0400/04/18 83743

-

RJ45 Connector Gid: Pinout, fil elektrik, Kalite Kab, ak Itilizasyon

sou 1970/01/1 79538

-

Gid la ultim nan kòd koulè fil nan sistèm elektrik modèn

Fason sistèm elektrik nou yo itilize koulè yo pa sèlman pou sanble.Chak koulè fil kounye a endike yon fonksyon espesifik, fè li pi fasil yo idantifye ak okipe konpozan elektrik kòrèkteman pandan en...sou 1970/01/1 66948

-

Purge Valv Gid: Fonksyon, sentòm, tès, ak ranplasman pou pèfòmans motè optimal

Valv la weteur se yon pati enpòtan nan sistèm yon machin nan ki ede kenbe lè a pwòp pa jere vapè gaz yo anvan yo ka chape anba nan atmosfè a.Sa a pa sèlman ede anviwònman an pa diminye polisyon, me...sou 1970/01/1 63087

-

Kalite (q) Faktè: Ekwasyon ak aplikasyon

Faktè bon jan kalite a, oswa 'Q', se enpòtan lè tcheke ki jan byen endukteur ak rezonan travay nan sistèm elektwonik ki itilize frekans radyo (RF).'Q' mezire ki jan byen yon sikwi minimize pèt enèj...sou 1970/01/1 63028

-

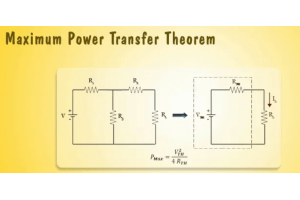

Atenn pèfòmans pik ak teyorèm nan transfè pouvwa maksimòm

Teyorèm maksimòm transfè pouvwa a eksplike kijan enèji ki sòti nan yon sous, tankou yon batri oswa dèlko, ap koule nan yon chaj ki konekte.Li montre kondisyon an egzak kote chaj la resevwa pouvwa k...sou 1970/01/1 54092

-

Espesifikasyon batri A23 ak konpatibilite

Batri a A23 se yon ti, silenn ki gen fòm batri ak vòltaj segondè.Yo te rele tou 23a, 23AE, oswa MN21, li kouri nan 12 vòlt ak pi wo pase AA oswa AAA pil.Konsepsyon espesyal li fè li pafè p...sou 1970/01/1 52171