HDL: Déblotché inovasyon nan konsepsyon sikwi dijital

Gid sa a eksplore deskripsyon pyès ki nan konpitè Lang (HDLs), zouti enpòtan pou vire desen abstrè nan reyèl, sikwi fabrike.Nou kouvri evolisyon yo, aplikasyon pou nan ASIC ak FPGA konsepsyon, ak enpak yo sou elektwonik modèn.Atravè egzanp ak Sur ekspè, gid sa a gen pou objaktif pou apwofondi konpreyansyon ou nan HDLs ak ranfòse tou de teyori ou ak ladrès pratik.Dekouvri kijan HDLS pon diferans ki genyen ant lide ak aparèy fizik, kondwi inovasyon nan teknoloji.Katalòg

Wòl HDL nan konsepsyon dijital

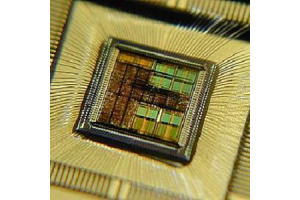

Materyèl Deskripsyon Lang (HDL) jwe yon wòl nan konsepsyon de sistèm dijital pa bay yon fason estriktire modèl sikwi konplèks.Li pèmèt yo kraze gwo sistèm nan pi piti, modil dosil, ki fè yo teste ak verifye lè l sèvi avèk elektwonik konsepsyon automatisation (EDA) zouti.Yon fwa valide, modil sa yo yo sentetiz nan Netlists Gate-nivo ak transfòme nan sikwi fizik nan ASIC oswa FPGA plasman ak routage.Lajman itilize nan endistri tankou Silisyòm Valley, HDL kondwi inovasyon nan ede balans konsepsyon kontrent ak solisyon kreyatif, fè li yon eleman kle nan avanse teknoloji dijital.

Devlopman istorik nan HDL

Devlopman nan pyès ki nan konpitè deskripsyon lang (HDLs) kouvri deseni, en soti nan fragmenté, zouti Tanporèman nich nan estanda, endistri-lajè solisyon tankou VHDL ak Verilog pa fen ane 1980 yo.Sa yo pratik estanda HDLS konsepsyon inifye ak kolaborasyon amelyore.Kòm teknoloji avanse, HDLs elaji pou sipòte sistèm pi konplèks, kenkayri ak konsepsyon lojisyèl ak nouvo lang tankou SystemC ak SuperLog.HDLS te montre valè yo nan amelyore kominikasyon, diminye erè, ak senplifye pwosesis la konsepsyon.Evolisyon an kontinyèl nan HDLs reflete bezwen an pou inovasyon kontinyèl satisfè demand yo chanje nan konsepsyon dijital pou devlopman teknoloji modèn.

Entansyon

Kòm sikwi entegre yo te grandi pi konplèks, kondwi pa lwa Moore a depi lane 1970 yo, metodoloji konsepsyon te deplase soti nan konsantre sou eleman endividyèl nan jere sistèm-nivo koule done ak distribisyon.Chanjman sa a mennen nan adopsyon an nan enskri transfè nivo (RTL) distraksyon, ki pèmèt yo konsantre sou fonksyon lojik ak distribisyon san yo pa bezwen adrese detay fabrikasyon bonè nan.RTL abstraction, ki te sipòte pa pyès ki nan konpitè deskripsyon lang (HDLs), rasyonalize pwosesis la konsepsyon pa balanse pèfòmans, pouvwa, ak évolutivité.Li diminye sik konsepsyon, amelyore kolaborasyon, epi li ede antisipe pwoblèm potansyèl, anpeche revizyon koute chè.Pa konsantre sou pi wo nivo distraksyon, ou déblotché pi gwo efikasite, adaptabilite, ak inovasyon nan jaden flè nan teknoloji rapidman en.

Karakteristik estriktirèl

Materyèl Deskripsyon Lang (HDLs) sèvi kòm fondasyon textuelle ki defini estrikti a, konpòtman, ak distribisyon nan sistèm sikwi.Yo fonksyone tankou lang pwogramasyon paralèl men yo espesyalman vizan nan direksyon jere distribisyon ak koneksyon pyès ki nan konpitè.HDLS opere atravè divès nivo distraksyon, estriktirèl, konpòtman, ak enskri-transfè, apwoche konsepsyon sikwi soti nan pèspektiv diferan.Nan nivo estriktirèl la, konpozan detay HDLS ak koneksyon, analogue nan chema.Nivo nan konpòtman konsantre sou sa ki kous la ta dwe fè, pandan y ap nivo a enskri-transfè (RTL) dekri koule done ak operasyon ant anrejistre, balanse fonctionnalités ak spesifik pyès ki nan konpitè.HDLS tou sipòte sentèz lojik, konvèti wo nivo desen nan Gate-nivo sikwi, ak simulation, ki tès fonctionnalités anvan deplwaman pyès ki nan konpitè.Kontrèman ak langaj pwogramasyon tradisyonèl yo, HDL yo se prensipalman modèl zouti ki pran konpòtman kenkayri, fè yo enpòtan pou egzat, konsepsyon sikwi inovatè.

Mennen ankèt sou koule done nan HDL

Kontrèman ak lang pwogramasyon tradisyonèl ki priyorite koule kontwòl, HDLs konsantre sou modèl koule done ak distribisyon nan sikwi pou devlopman pyès ki nan konpitè ak simulation.Kapasite inik sa a pran konpòtman tanporèl la nan pyès ki nan konpitè ansanm HDLS apa de lang tankou C ++.HDL modèn, tankou SystemVerilog, yo se de pli zan pli melanje paradigms pwogramasyon, enkòpore objè-oryante konsèp amelyore modularite ak antretyen nan desen sistèm konplèks.HDLs tou jwe yon wòl nan sentèz lojik, transfòme deskripsyon wo nivo nan pòtay-nivo en, asire ke desen abstrè aliman ak kontrent fizik.Anplis de sa, ki pa synthesizable eleman HDL yo te itilize pou simulation ak verifikasyon nan rijid tès sikwi tès anvan pwodiksyon.Kòm HDLs kontinye evolye yo, yo gen plis chans yo adopte plis lojisyèl-tankou karakteristik nan adrès ap grandi kenkayri complexités, Tranzisyon diferans ki genyen ant presizyon pyès ki nan konpitè ak distraksyon zanmitay.

Amelyore konsepsyon sikwi entegre ak HDL

Materyèl Deskripsyon Lang (HDLs) rasyonalize pwosesis la konplèks nan konsepsyon sikwi entegre pa transfòme lide abstrè nan pratik, plan ègzèkutabl.Anpil souvan itilize òganigram ak dyagram eta a kat soti lojik sikwi anvan konvèti li nan egzak kòd HDL, anpil tankou kreye plan pou konstriksyon.Pandan ke konfòme yo avèk kondisyon sikwi, lòt moun pote style inik yo nan kodaj pa enkòpore algoritm ak scripting senplifye travay repetitif.Erè tcheke zouti Lè sa a, idantifye pwoblèm bonè, asire fyabilite anvan sentèz.Apre sentèz, netlist yo ap prepare pou manifakti, si wi ou non pou FPGAs oswa ASICs, ki konsantre sou espesifikasyon aparèy pou fè pou evite defi pwodiksyon an.HDLS frape yon balans ant kreyativite ak presizyon, pèmèt inovatè ankò serye desen sikwi ki avèk efikasite pwogrè soti nan konsèp nan realizasyon fizik.

Sou nou

ALLELCO LIMITED

Li piplis

Quick Inquiry

Tanpri voye yon ankèt, nou pral reponn imedyatman.

Vitis Inifye lojisyèl platfòm: Akselere sistèm entegre ak informatique adaptasyon ak xilinx

sou 2025/01/7

Evolisyon an ak pwogrè estratejik nan teknoloji VLSI

sou 2025/01/6

Posts popilè

-

Enstriksyon konplèks Set Odinatè: Ki jan yo chanje informatique?

sou 8000/04/19 147781

-

USB-C pinout ak karakteristik

sou 2000/04/19 112062

-

Sèvi ak Xilinx Inifye Simulation Primitif: Yon Gid konplè nan FPGA Design ak Simulation

sou 1600/04/19 111352

-

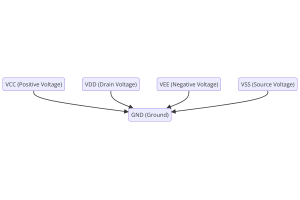

Tansyon ekipman pou pouvwa nan elektwonik: siyifikasyon VCC, VDD, VEE, VSS, ak GND

sou 0400/04/19 83816

-

RJ45 Connector Gid: Pinout, fil elektrik, Kalite Kab, ak Itilizasyon

sou 1970/01/1 79630

-

Gid la ultim nan kòd koulè fil nan sistèm elektrik modèn

Fason sistèm elektrik nou yo itilize koulè yo pa sèlman pou sanble.Chak koulè fil kounye a endike yon fonksyon espesifik, fè li pi fasil yo idantifye ak okipe konpozan elektrik kòrèkteman pandan en...sou 1970/01/1 66998

-

Purge Valv Gid: Fonksyon, sentòm, tès, ak ranplasman pou pèfòmans motè optimal

Valv la weteur se yon pati enpòtan nan sistèm yon machin nan ki ede kenbe lè a pwòp pa jere vapè gaz yo anvan yo ka chape anba nan atmosfè a.Sa a pa sèlman ede anviwònman an pa diminye polisyon, me...sou 1970/01/1 63124

-

Kalite (q) Faktè: Ekwasyon ak aplikasyon

Faktè bon jan kalite a, oswa 'Q', se enpòtan lè tcheke ki jan byen endukteur ak rezonan travay nan sistèm elektwonik ki itilize frekans radyo (RF).'Q' mezire ki jan byen yon sikwi minimize pèt enèj...sou 1970/01/1 63057

-

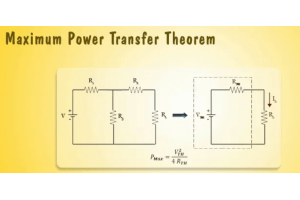

Atenn pèfòmans pik ak teyorèm nan transfè pouvwa maksimòm

Teyorèm maksimòm transfè pouvwa a eksplike kijan enèji ki sòti nan yon sous, tankou yon batri oswa dèlko, ap koule nan yon chaj ki konekte.Li montre kondisyon an egzak kote chaj la resevwa pouvwa k...sou 1970/01/1 54097

-

Espesifikasyon batri A23 ak konpatibilite

Batri a A23 se yon ti, silenn ki gen fòm batri ak vòltaj segondè.Yo te rele tou 23a, 23AE, oswa MN21, li kouri nan 12 vòlt ak pi wo pase AA oswa AAA pil.Konsepsyon espesyal li fè li pafè p...sou 1970/01/1 52208