XC4VLX100-10FFG1148C FPGA: Karakteristik, espesifikasyon, aplikasyon ak gid pwogramasyon

Si ou ap travay ak desen dijital konplèks, XC4VLX100-10FFG1148C a ba ou pouvwa a ak fleksibilite ou bezwen.Sa a FPGA pake segondè kapasite lojik, bati-an memwa, ak yon gwo kantite I/O broch, fè li ideyal pou mande aplikasyon yo.Nan gid sa a, ou pral aprann sou karakteristik li yo, pèfòmans, paramèt distribisyon, aplikasyon pou, etap pwogramasyon, avantaj ak dezavantaj, detay anbalaj, ak background manifakti.Katalòg

Ki sa ki XC4VLX100-10FFG1148C a?

A XC4VLX100-10FFG1148C se yon FPGA pèfòmans-wo soti nan Xilinx (kounye a AMD), ki fè pati fanmi an Virtex-4 LX, ki te bati sou yon pwosesis kwiv 90 nm.Aparèy sa a fèt pou aplikasyon konplèks lojik dijital ak se yon pati nan seri a LX ki mete aksan sou lojik ak resous memwa san yo pa resèpteur seri segondè-vitès.Idantifye pa 1148-boul li yo FCBGA pake ak Rating tanperati komèsyal yo, li reprezante youn nan opsyon ki pi wo-kapasite nan pwogramasyon an LX.

Kap chèche XC4VLX100-10FFG1148C?Kontakte nou yo tcheke stock aktyèl, tan plon, ak prix.

XC4VLX100-10FFG1148C karakteristik

• Segondè kapasite lojik

XC4VLX100-10FFG1148C a bay 110,592 selil lojik, ki pèmèt aplikasyon an nan desen konplèks dijital sou yon aparèy sèl.Sa a kapasite lojik gwo fè li apwopriye pou pwosesis segondè-dansite ak fonksyon kontwòl.

• Embedded ak distribye memwa

Li entegre alantou 4.22 Mbits nan memwa total, konbine blòk RAM ak distribye RAM.Sa a achitekti memwa sipòte depo done efikas, tampon, ak sou-chip pwosesis san yo pa bezwen an pou anpil memwa ekstèn.

• Anpil resous I/O

Aparèy la ofri 768 itilizatè I/O broch, bay fleksibilite nan koòdone ak divès kalite konpozan ekstèn ak sistèm.Sa yo mwen/OS sipòte nan yon pakèt domèn estanda nan karakteristik nan Seletio ™, amelyore tablo-nivo koneksyon.

• High-pèfòmans nwayo

Opere nan yon vòltaj nwayo 1.2 V, FPGA a sipòte entèn clocking jiska apeprè 500 megaèrts, fournir pèfòmans lojik vit.Sa a asire operasyon serye nan mande aplikasyon pou gwo vitès.

• Ranje tanperati komèsyal yo

Rated pou 0 ° C a +85 ° C, se aparèy la ki fèt pou anviwònman komèsyal-klas.Li kenbe pèfòmans ki estab nan tout kondisyon opere tipik pou sistèm endistriyèl ak entegre.

Referans Paramèt distribisyon revèy

Dyagram nan montre monte nan revèy ak mezi tan otòn pou XC4VLX100-10FFG1148C a, ki konsantre sou TRclk (monte tan) ak tFCLK (tan tonbe) ant 20% ak 80% nivo vòltaj nan siyal la revèy.Li montre ki jan byen vit revèy la tranzisyon soti nan ki ba a segondè ak segondè a ki ba, ki se gwo pou kenbe entegrite distribisyon ak operasyon serye nan FPGA la.Kontwòl egzak nan bor sa yo asire senkronizasyon egzat nan lojik entèn ak interfaces ekstèn.Nan XC4VLX100-10FFG1148C a, kenbe bon ogmantasyon ak fwa otòn lan enpòtan pou pèfòmans ki estab gwo vitès ak minimize deformation siyal.

Enstalasyon tès jeneralize

Dyagram lan montre konfigirasyon tès jeneralize yo itilize pou mezire reta pwodiksyon ak karakteristik siyal nan XC4VLX100-10FFG1148C FPGA.Yon rezistans referans (rRef) ak kondansateur (cRef) yo ki konekte nan pwodiksyon an FPGA, ak VMezi ki reprezante nivo vòltaj la nan ki mezi distribisyon yo te pran.Sa a konfigirasyon estanda asire mezi ki konsistan ak egzat nan reta tranzisyon siyal atravè anviwònman tès diferan.Pou XC4VLX100-10FFG1148C a, sa enpòtan pou validation pèfòmans I/O gwo vitès ak asire aparèy la satisfè espesifikasyon distribisyon nan aplikasyon pou reyèl.

XC4VLX100-10FFG1148C Espesifikasyon

|

Lèt |

Paramèt |

|

Fabrikan |

Am/xilinx |

|

Seri |

Virtex®-4 LX |

|

Anbalaj |

Plato |

|

Estati pati |

Aktif |

|

Kantite laboratwa/CLBS |

12288 |

|

Kantite eleman lojik/selil |

110592 |

|

Total Bits Ram |

4423680 |

|

Kantite I/O |

768 |

|

Vòltaj - Pwovizyon pou |

1.14 V ~ 1.26 V |

|

Kalite aliye |

Sifas mòn |

|

Tanperati opere |

0 ° C ~ 85 ° C (TJ) |

|

Pake / Ka |

1148-BBGA, FCBGA |

|

Pake aparèy founisè |

1148-FCPBGA (35 × 35) |

|

Nimewo pwodwi baz |

Xc4vlx100 |

XC4VLX100-10FFG1148C Aplikasyon

1. Sistèm siyal dijital (DSP)

XC4VLX100-10FFG1148C a byen adapte pou mete ann aplikasyon algoritm DSP pèfòmans-wo gras a gwo kapasite lojik li yo ak memwa entegre.Ou ka bati tuyaux pwosesis koutim ki okipe kalkil entansif nan tan.Sa fè li ideyal pou aplikasyon tankou pwosesis imaj, sistèm rada, ak filtraj avanse.

2. akselerasyon sistèm entegre

Avèk achitekti fleksib li yo, se aparèy la lajman itilize akselere fonksyon sistèm entegre tankou manyen pwotokòl, jesyon otobis, ak pyès ki nan konpitè offloading.Pa chanje travay soti nan lojisyèl FPGA twal, li amelyore reyaksyon sistèm lan.Sa a pèmèt yo optimize pèfòmans pandan w ap kenbe fleksibilite konsepsyon.

3. Kominikasyon ak Ekipman Rezo

Segondè I/O konte FPGA a ak kapasite pwosesis fè li apwopriye pou enfrastrikti kominikasyon, ki gen ladan switch, routeurs, ak pon koòdone.Li ka jere pwotokòl rezo konplèks ak gwo-Pleasant done sous dlo ak latansi ki ba.Sa fè li yon chwa serye pou rezo zo rèl ak sistèm sant done.

4. High-vitès done akizisyon ak pwosesis

XC4VLX100-10FFG1148C a èksèl nan aplikasyon ki mande pou done rapid kaptire ak pwosesis, tankou instrumentation ak ekipman syantifik.Memwa entegre li yo ak resous lojik pèmèt vit tampon ak manipilasyon done paralèl.Sa a asire manyen efikas nan komèsan done gwo nan anviwònman.

Xc4vlx100-10ffg1148c pati menm jan an

|

Spesifikasyon |

XC4VLX100-10FFG1148C |

Xc4vlx100-10ffg1148i |

XC4VLX100-11FFG1148C |

Xc4vlx100-10ff1148c |

XC4VLX100-10FFG1513C |

XC4VLX100-12FFG1148C |

|

Fabrikan |

Xilinx (AMD) |

Xilinx (AMD) |

Xilinx (AMD) |

Xilinx (AMD) |

Xilinx (AMD) |

Xilinx (AMD) |

|

Fanmi |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

|

Kapasite lojik |

110,592 selil |

110,592 selil |

110,592 selil |

110,592 selil |

110,592 selil |

110,592 selil |

|

Kalite pake |

Fcbga |

Fcbga |

Fcbga |

Fcbga |

Fcbga |

Fcbga |

|

Boul konte |

1148 |

1148 |

1148 |

1148 |

1513 |

1148 |

|

Vitès |

–10 |

–10 |

–11 |

–10 |

–10 |

–12 |

|

Klas tanperati |

Komèsyal (C) |

Endistriyèl (mwen) |

Komèsyal (C) |

Komèsyal (C) |

Komèsyal (C) |

Komèsyal (C) |

|

Nwayo vòltaj |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

|

Operasyon ranje tanperati |

0 ° C a +85 ° C |

–40 ° C a +100 ° C |

0 ° C a +85 ° C |

0 ° C a +85 ° C |

0 ° C a +85 ° C |

0 ° C a +85 ° C |

|

Diferans |

Baz pati, estanda pkg |

Sipò pou temp endistriyèl |

Pi wo klas vitès |

Manke "G" deziyasyon |

Pi gwo pake, plis I/O |

Pi rapid klas vitès nan seri |

Xc4vlx100-10ffg1148c etap pwogramasyon

Anvan pwogramasyon XC4VLX100-10FFG1148C a, ou bezwen asire ke anviwònman devlopman ou ak dosye konfigirasyon yo byen mete kanpe.Aparèy la sipòte mòd konfigirasyon miltip, se konsa chwazi youn nan dwa byen bonè asire yon pwosesis pwogramasyon lis ak siksè.

1. Pouvwa moute aparèy la

Kòmanse pa aplike pouvwa a FPGA a lè l sèvi avèk ray yo vòltaj yo mande yo (vccint, vccaux, ak vcc_config).Ou dwe asire w ke tension sa yo rive nan nivo ki estab anvan nenpòt konfigirasyon kòmanse.Bon pouvwa sekans se yon bon bagay pou fè pou evite erè inisyalizasyon.

2. Chwazi mòd konfigirasyon

Next, FPGA echantiyon yo mòd broch li yo nan kwen an ap monte nan init_b detèmine ki metòd konfigirasyon yo itilize.Ou ka chwazi nan jtag, esklav seri, seri mèt, oswa seleksyon, tou depann de konfigirasyon ou.Asire w ke broch yo mòd yo mete kòrèkteman, menm jan yo kontwole ki jan yo pral Bitstream a dwe chaje.

3. Inisyalize aparèy la

FPGA a efase memwa konfigirasyon li yo ak prepare pou loading Bitstream pandan inisyalizasyon.Nan faz sa a, siyal tankou INIT_B, GWE, ak GTS yo te itilize yo mete aparèy la nan yon eta li te ye.Ou ta dwe asire ke tout siyal inisyalizasyon konpòte yo jan yo espere anvan yo kontinye.

4. Chaje Bitstream la

Sèvi ak koòdone ou chwazi a, ou kounye a kouran bitstream nan konfigirasyon nan FPGA la.Pou egzanp, si lè l sèvi avèk JTAG, se bitstream a deplase seri nan memwa konfigirasyon aparèy la.Transfè egzat ak konplè Bitstream ki nesesè pou pwogram siksè.

5. Kòmanse pwosesis la konfigirasyon

Yon fwa se bitstream a konplètman chaje, FPGA a sòti mòd chanjman ak kòmanse sekans lan demaraj.Yon lòd jstart oswa pwosesis ekivalan deklannche aparèy la finalize konfigirasyon.Ou dwe pèmèt FPGA a ranpli etap sa a san entèripsyon.

6. Konfigirasyon konplè ak antre nan mòd itilizatè

FPGA a otomatikman tcheke entegrite nan Bitstream lè l sèvi avèk CRC ak, si valab, afime siyal la fè.Yon fwa sa rive, lojik itilizatè vin aktif, ak aparèy la opere dapre konsepsyon ou.Nan pwen sa a, pwosesis la konfigirasyon se konplè, ak FPGA a se konplètman fonksyonèl.

7. Verifikasyon si ou vle

Finalman, ou ka fè yon readback oswa etap verifikasyon asire konfigirasyon an te gen siksè.Sa a ka fè nan JTAG oswa SelectMap, tou depann de mòd ou te itilize a.Malgre ke si ou vle, li la trè rekòmande pou sistèm konfime pwogramasyon apwopriye.

Xc4vlx100-10ffg1148c avantaj ak dezavantaj

Avantaj

• Pi ba konsomasyon pouvwa jeneral konpare ak anpil 90 nm FPGAs.

• Sipòte pa yon ekosistèm konsepsyon ki gen matirite ak ki estab.

• Pwopòsyon fò pèfòmans-a-pri pou jenerasyon li yo.

• Achitekti modilè ASMBL amelyore efikasite konsepsyon.

• Serye, pwouve platfòm pou lontan-etabli desen.

Dezavantaj

• Baze sou teknoloji eritaj ak sipò nan lavni limite.

• manke resèpteur seri gwo vitès yo te jwenn nan plus fanmi yo.

• Pi ba évolutivité ak fleksibilite konpare ak FPGA modèn.

• Defi potansyèl pou apwovizyone akòz laj pwodwi.

• Mande pou pouvwa atansyon ak jesyon tèmik nan itilizasyon segondè.

Xc4vlx100-10ffg1148c dimansyon anbalaj

|

Paramèt |

Dimansyon |

|

Kalite pake |

FFG1148 (Flip-chip amann-pitch BGA) |

|

Anplasman boul |

1.00 mm |

|

Pake gwosè kò (L × W) |

35.00 mm × 35.00 mm |

|

Pake gwosè kò (L × W, pous) |

1.378 nan × 1.378 nan |

|

An jeneral wotè pake (a) |

3.40 mm (tipik) |

|

An jeneral wotè pake (A, pous) |

0.134 nan (tipik) |

|

Tolerans gwosè kò |

± 0.20 mm |

|

Etalaj boul |

34 × 34 (1.00 mm kadriyaj ton) |

|

Boul konte |

1,148 voye boul |

|

Dyamèt boul (nominal) |

0.60 mm |

|

Epesè substrate (b) |

~ 1.00 mm |

|

Wotè kanpe (A1) |

0.40 mm (nominal) |

|

Chalè paresseux / metal gwosè bouchon |

~ 32 mm kare (tipik tèt metal zòn) |

|

Kalite aliye |

Sifas mòn |

Xc4vlx100-10ffg1148c manifakti

XC4VLX100-10FFG1148C a manifaktire pa Xilinx, yon pyonye nan jaden an nan aparèy lojik pwogramasyon.Nan 2022, xilinx te vin yon pati nan AMD (Avanse aparèy mikwo), plis ranfòse pozisyon li nan pèfòmans-wo informatique ak teknoloji adaptasyon.Fizyon sa a konbine ekspètiz FPGA Xilinx a ak lidèchip pwosesis AMD a, asire gaya sipò alontèm ak inovasyon pou pwodwi tankou XC4VLX100-10FFG1148C la.

Konklizyon

XC4VLX100-10FFG1148C a vle di soti pou konte gwo selil lojik li yo, achitekti memwa fleksib, lajè I/O kapasite, ak pèfòmans solid nan jenerasyon li yo.Li sipòte segondè-vitès clocking ak serye entegrite siyal, fè li byen adapte pou mande aplikasyon pou nan DSP, rezo, ak sistèm entegre.Pandan ke li ofri estabilite pwouve ak yon ekosistèm ki gen matirite, li reflete teknoloji eritaj ak kèk évolutivité ak limit apwovizyone, fè atansyon konsiderasyon enpòtan pou desen modèn.

Fich pdf

XC4VLX100-10FFG1148C FACASHEETS:

Sou nou

ALLELCO LIMITED

Li piplis

Quick Inquiry

Tanpri voye yon ankèt, nou pral reponn imedyatman.

Kesyon yo poze souvan [FAQ]

1. Kijan XC4VLX100-10FFG1148C yo konpare ak plus fanmi FPGA yo?

Fanmi plus tankou Virtex-6, 7-seri, oswa Ultrascale ofri pi gwo vitès, pi ba pouvwa, ak resèpteur seri entegre.Sepandan, XC4VLX100-10FFG1148C a bay ekselan valè pou sistèm eritaj ki estab ki pa mande pou karakteristik yo ki dènye.

2. Ki zouti devlopman yo konpatib ak XC4VLX100-10FFG1148C a?

Ou ka itilize Xilinx ISE konsepsyon suite pou sentèz, aplikasyon, ak jenerasyon Bitstream.Depi sa a se yon fanmi ki pi gran FPGA, plus zouti tankou Vivado pa sipòte li, se konsa asire w ke ou gen yon anviwònman devlopman konpatib.

3. Èske ou ka itilize XC4VLX100-10FFG1148C nan anviwònman tanperati-sansib?

Se aparèy sa a rated pou yon seri tanperati komèsyal nan 0 ° C a +85 ° C, fè li apwopriye pou pi estanda kondisyon endistriyèl ak entegre.Pou anviwònman pi di, yo ka yon vèsyon ki gen yon seri pwolonje ranje.

4. Èske XC4VLX100-10FFG1148C a dwe itilize pou aplikasyon pou pwosesis done gwo vitès?

Wi.Avèk yon revèy entèn 500 megaèrts ak gwo kapasite lojik, li okipe gwo vitès pwosesis siyal avèk efikasite.Sepandan, ou pral bezwen konsepsyon bon kontrent distribisyon ak tablo-nivo kouman yo maksimize pèfòmans.

5. Èske XC4VLX100-10FFG1148C a mande pou refwadisman espesyal oswa jesyon tèmik?

Nan itilizasyon segondè, FPGA sa a ka jenere chalè enpòtan.Ou ta dwe bay bon vantilasyon, heatsinks, oswa tablo-nivo konsepsyon tèmik yo kenbe pèfòmans ak evite etalaj oswa alontèm domaj.

BCM5221KPB Ethernet PHY: karakteristik, dyagram blòk, aplikasyon ak fich

sou 2025/10/12

Ki jan yo chwazi vit-kònen ak ralanti-kònen fuzibl pwoteje sikwi pouvwa

sou 2025/10/11

Posts popilè

-

Enstriksyon konplèks Set Odinatè: Ki jan yo chanje informatique?

sou 8000/04/17 147713

-

USB-C pinout ak karakteristik

sou 2000/04/17 111758

-

Sèvi ak Xilinx Inifye Simulation Primitif: Yon Gid konplè nan FPGA Design ak Simulation

sou 1600/04/17 111324

-

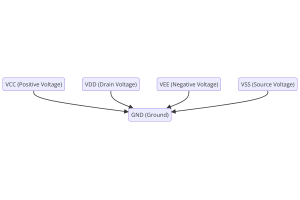

Tansyon ekipman pou pouvwa nan elektwonik: siyifikasyon VCC, VDD, VEE, VSS, ak GND

sou 0400/04/17 83639

-

RJ45 Connector Gid: Pinout, fil elektrik, Kalite Kab, ak Itilizasyon

sou 1970/01/1 79300

-

Gid la ultim nan kòd koulè fil nan sistèm elektrik modèn

Fason sistèm elektrik nou yo itilize koulè yo pa sèlman pou sanble.Chak koulè fil kounye a endike yon fonksyon espesifik, fè li pi fasil yo idantifye ak okipe konpozan elektrik kòrèkteman pandan en...sou 1970/01/1 66793

-

Kalite (q) Faktè: Ekwasyon ak aplikasyon

Faktè bon jan kalite a, oswa 'Q', se enpòtan lè tcheke ki jan byen endukteur ak rezonan travay nan sistèm elektwonik ki itilize frekans radyo (RF).'Q' mezire ki jan byen yon sikwi minimize pèt enèj...sou 1970/01/1 62958

-

Purge Valv Gid: Fonksyon, sentòm, tès, ak ranplasman pou pèfòmans motè optimal

Valv la weteur se yon pati enpòtan nan sistèm yon machin nan ki ede kenbe lè a pwòp pa jere vapè gaz yo anvan yo ka chape anba nan atmosfè a.Sa a pa sèlman ede anviwònman an pa diminye polisyon, me...sou 1970/01/1 62845

-

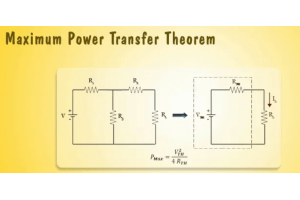

Atenn pèfòmans pik ak teyorèm nan transfè pouvwa maksimòm

Teyorèm maksimòm transfè pouvwa a eksplike kijan enèji ki sòti nan yon sous, tankou yon batri oswa dèlko, ap koule nan yon chaj ki konekte.Li montre kondisyon an egzak kote chaj la resevwa pouvwa k...sou 1970/01/1 54038

-

Espesifikasyon batri A23 ak konpatibilite

Batri a A23 se yon ti, silenn ki gen fòm batri ak vòltaj segondè.Yo te rele tou 23a, 23AE, oswa MN21, li kouri nan 12 vòlt ak pi wo pase AA oswa AAA pil.Konsepsyon espesyal li fè li pafè p...sou 1970/01/1 52019