EP2S60F672C4 FPGA: Karakteristik, Aplikasyon, Pwogramasyon & Fèy Gid

Nan gid sa a, ou pral jwenn yon BECA klè nan EP2S60F672C4 a, yon FPGA pwisan soti nan Intel a Stratix II fanmi an.Ou pral aprann sou karakteristik prensipal li yo, achitekti, estrikti blòk, ak karakteristik teknik yo konprann ki jan li adapte nan avanse desen dijital.Li te tou mache ou nan etap pwogramasyon li yo, aplikasyon pou, avantaj, ak dezavantaj pou ou ka wè egzakteman ki kote ak ki jan yo ka itilize aparèy sa a.Katalòg

Ki sa ki EP2S60F672C4 la?

A EP2S60F672C4 se yon FPGA dansite ki soti nan Intel (ansyen Altera), ki fè pati fanmi Stratix II a.Bati sou yon 90 nm, 1.2 v kòb kwiv mete SRAM pwosesis, li delivre sibstansyèl kapasite lojik nan yon pake 672-boul FBGA, fè li ideyal pou sistèm dijital konplèks.Kòm yon pati nan seri a EP2S, "60" aparèy la chita nan ranje a mitan-a-anwo nan pwogramasyon an Stratix II, ofri yon balans fò nan dansite lojik, entegre memwa, ak I/O resous yo.Li te ye pou achitekti gaya li yo ak fyab, sa a FPGA rete yon chwa ou fè konfyans nan anpil desen avanse.

Kap chèche EP2S60F672C4?Kontakte nou yo tcheke stock aktyèl, tan plon, ak prix.

Ep2S60F672C4 CAD Modèl

EP2S60F672C4 senbòl

EP2S60F672C4 anprint

EP2S60F672C4 3D modèl

EP2S60F672C4 Karakteristik

• Avanse 90 nm, 1.2 V pwosesis CMOS

EP2S60F672C4 se fabrike sou yon 90 nm tout-kouch kwiv CMOS pwosesis ki kouri nan yon 1.2 V nwayo vòltaj.Teknoloji sa a pèmèt gwo vitès, konsomasyon pouvwa redwi, ak pi gwo dansite lojik konpare ak pi gran jenerasyon FPGA.

• Adaptatif Lojik Modil (ALM) Achitèk

Aparèy la sèvi ak kichòy kòm blòk bilding lojik li yo olye pou yo eleman lojik tradisyonèl yo.Achitèk sa a amelyore itilizasyon resous, sa ki pèmèt fonksyon lojik pi konplèks yo dwe aplike avèk efikasite nan menm zòn nan Silisyòm.

• Segondè dansite lojik

Avèk apeprè 60,440 eleman lojik (24,176 kichòy), FPGA a sipòte gwo ak sofistike desen dijital.Kapasite sa a segondè fè li apwopriye pou aplikasyon pou tankou pwosesis siyal, kominikasyon, ak sistèm kontwòl entegre.

• Trimatrix ™ sou-chip memwa

EP2S60F672C4 entegre twa kalite blòk RAM, (M512, M4K, ak M-RAM) pou bay yon total alantou 2.4 Mbits nan memwa entegre.Sa a melanj pèmèt aplike ti FIFOs, mwayen tanpon, ak gwo double-pò souvni avèk efikasite.

• Blòk dedye DSP

Aparèy la gen ladan 36 dedye blòk DSP ki fèt pou operasyon aritmetik tankou miltiplikasyon, akimilasyon, ak filtraj FIR.Blòk sa yo ranfòse pèfòmans nan travay kalkil-entansif pandan y ap ekonomize resous lojik jeneral.

• High-vitès I/O ak siyal entegrite

Li sipòte divès kalite sèl-te fini ak diferans I/O estanda ansanm ak aliyman faz dinamik (DPA) sikwiyèr.Karakteristik sa yo pèmèt ki estab, gwo vitès done transfere jiska 1 Gbps, asire kominikasyon serye ak eleman ekstèn.

• Rich ekstèn memwa koòdone sipò

FPGA a se konpatib ak DDR, DDR2, QDR II, RLDRAM II, ak lòt estanda memwa.Bati-an koòdone sipò senplifye konsepsyon tablo ak reyalize done segondè debi pou aplikasyon pou memwa-entansif.

• Jesyon revèy fleksib

Jiska 12 sou-chip PLLs pèmèt miltiplikasyon revèy, divizyon, faz chanjman, ak glitch-gratis switchover.Ou ka amann-melodi revèy domèn ak diminye jitter, sipòte frekans revèy entèn ki rive jiska 500-550 megaèrts.

• Bitstream chifreman ak rkonfigurasyon

EP2S60F672C4 sipòte AES ki baze sou bitstream chifreman an sekirite pwopriyete entelektyèl.Li ofri tou kapasite aleka rkonfigurasyon, pèmèt nan-jaden dènye san yo pa ranplase aparèy la.

Stratix II Dyagram blòk

Dyagram blòk Stratix II a, jan yo montre pou EP2S60F672C4, montre aranjman entèn nan lojik, memwa, ak resous DSP ki fòme nwayo FPGA a.Blòk etalaj lojik (laboratwa) yo ranje nan yon griy regilye, ki te antoure pa kolòn RAM ak DSP entegre, ki bay vit aritmetik ak sou-chip kapasite depo.Periferik I/O eleman ak rezo revèy ankadreman estrikti sa a, pèmèt efikas transfè done ak kontwòl distribisyon ant FPGA a ak aparèy ekstèn.Dyagram sa a enpòtan paske li ede konprann kijan diferan blòk fonksyonèl yo òganize fizikman, sa ki pèmèt yo optimize plasman, routage, ak pèfòmans sistèm jeneral.

Stratix II I/O Banks Dyagram

Sa a Stratix II I/O dyagram bank montre ki jan broch yo opinyon/pwodiksyon nan EP2S60F672C4 yo gwoupe ak sa ki estanda elektrik chak gwoup sipòte.Chak bank I/O fèt pou okipe nivo vòltaj espesifik, kalite siyal, ak fonksyon tankou LVTTL, SSTL, LVD, oswa estanda opinyon revèy.Layout la montre ki jan diferan bank (eg, 1, 2, 5, 6 vs 3, 4, 7, 8, elatriye) yo optimisé pou swa jeneral-bi I/O oswa gwo vitès diferans siyal, ki gen ladan sipò pou LVDs/LVPECL entrain revèy nan bor yo.Konprann estrikti sa a enpòtan lè plase broch, paske bon seleksyon labank asire konpatibilite elektrik, senplifye routage tablo, ak maksimize pèfòmans FPGA a nan gwo vitès desen.

EP2S60F672C4 Espesifikasyon

|

Lèt |

Paramèt |

|

Fabrikan |

Altera/Intel |

|

Seri |

Stratix® II |

|

Anbalaj |

Plato |

|

Estati pati |

Demode |

|

Kantite laboratwa/CLBS |

3022 |

|

Kantite eleman lojik/selil |

60,440 |

|

Total Bits Ram |

2,544,192 |

|

Kantite I/O |

492 |

|

Vòltaj - Pwovizyon pou |

1.15 V ~ 1.25 V |

|

Kalite aliye |

Sifas mòn |

|

Tanperati opere |

0 ° C ~ 85 ° C (TJ) |

|

Pake / Ka |

672-BBGA |

|

Pake aparèy founisè |

672-FBGA (27 × 27) |

|

Nimewo pwodwi baz |

EP2S60 |

EP2S60F672C4 Aplikasyon

1. Processing siyal dijital (DSP) ak filtraj

EP2S60F672C4 se byen adapte pou mete ann aplikasyon pèfòmans-wo fonksyon DSP tankou FIR ak filtè IIR, pwosesis FFT, ak operasyon aritmetik konplèks.Blòk DSP dedye li yo okipe miltiplikasyon ak akimilasyon avèk efikasite, libere resous lojik jeneral pou lòt travay.Memwa a sou-chip Trimatrix ™ pèmèt lis done tampon ak pipelining, ki se gwo pou pwosesis an tan reyèl nan pousantaj echantiyon segondè.Sa fè aparèy la ideyal pou avanse odyo, videyo, ak aplikasyon pou siyal rada.

2. Kominikasyon gwo vitès ak rezo

FPGA a gwo vitès I/O interfaces ak dinamik faz aliyman (DPA) sikwi sipò serye, Gigabit-nivo done transmisyon.Li ka aplike pwotokòl kominikasyon ak fonksyon kouch fizik pou sistèm tankou routeurs, switch, ak backplane konekte.Avèk gwo kapasite lojik li yo ak PLL fleksib, li ka jere distribisyon konplèks ak konvèsyon pwotokòl ant miltip interfaces gwo vitès.Kapasite sa yo fè li yon anfòm fò pou enfrastrikti telecom ak ekipman rezo wo-band.

3. Contrôleur memwa ak sistèm pwosesis done

EP2S60F672C4 sipòte divès kalite interfaces memwa ekstèn ki gen ladan DDR, DDR2, RLDRAM II, ak QDR II, fè li ideyal pou konsepsyon contrôleur memwa segondè-band.Li ka okipe done tampon, adrese jenerasyon, ak abitraj nan vitès ki wo ak latansi minim.Konbinezon an nan rezo revèy vit ak blòk RAM entegre pèmèt jesyon efikas nan sous dlo gwo.Sa fè FPGA a apwopriye pou pwosesis imaj, difizyon videyo, ak tribin kalkil syantifik ki konte sou debi done lou.

4. Lojik koutim ak akselerasyon entegre

Avèk plis pase 60,000 eleman lojik ak jesyon revèy rich, FPGA a ka òganize Customized akseleratè kenkayri pou algoritm espesifik.Konsèpteur souvan itilize li nan debake travay kalkil entansif soti nan proseseur, tankou chifreman, analiz pwotokòl, oswa pasan kontwòl an tan reyèl.Li kapab tou entegre plizyè blòk fonksyonèl, fè li apwopriye pou konplèks Soc-tankou desen.Fleksibilite sa a fè li valab nan aplikasyon tankou automatisation endistriyèl, sistèm sekirite, ak inite kontwòl avyon.

5. Pwototip ak Edikasyon Devlopman tribin

Se aparèy la EP2S60 souvan yo te jwenn sou twous devlopman FPGA itilize pou pwototip, tès, ak rechèch akademik yo.Balans li nan kapasite lojik, I/O konte, ak kapasite DSP pèmèt enjenyè ak elèv yo aplike ak verifye sistèm plen sou yon chip sèl.Li sipòte iterasyon rapid nan desen dijital, pèmèt verifikasyon pyès ki nan konpitè anvan yo komèt nan devlopman ASIC.Anpil inivèsite ak R & D laboratwa itilize li yo anseye avanse konsepsyon dijital ak konsèp pwosesis siyal.

EP2S60F672C4 Pati ki sanble

|

Spesifikasyon |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

Fanmi / Seri |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

|

Eleman Lojik (LE) |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

|

Swak |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

|

Pakèt |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

Vitès |

C4 (STD) |

C3 (pi vit) |

C5 (pi vit) |

C5 (pi vit) |

I4 (STD) |

I3 (pi vit) |

|

Klas tanperati |

Komèsyal (0 ~ 70 ° C) |

Komès |

Komès |

Komès |

Endistriyèl (−40 ~ 100 ° C) |

Endistriyèl (−40 ~ 100 ° C) |

|

Mwen/o broch |

492 |

492 |

492 |

492 |

492 |

492 |

|

Sou-chip memwa |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

|

Nwayo vòltaj |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

|

Kle diferans |

Debaz vitès komèsyal yo |

C3 vitès bin, plon-gratis "n" |

Pi wo vitès bin |

Pi wo vitès bin, "n" Variant |

Tanperati endistriyèl, menm dansite |

Endistriyèl, pi vit vitès, plon-gratis |

EP2S60F672C4 Pwogramasyon Etap

Anvan ou ka itilize EP2S60F672C4 FPGA a nan konsepsyon ou, ou bezwen byen configured li ak Bitstream konpile ou.Pwosesis sa a enplike nan prepare dosye a pwogramasyon, mete kanpe koòdone nan kenkayri, ak asire ke konfigirasyon an charj kòrèkteman sou pouvwa-up.

Etap 1: Kreye ak konpile konsepsyon ou

Ou kòmanse pa devlope konsepsyon lojik ou lè l sèvi avèk Intel Quartus II lojisyèl.Apre w fin ranpli konsepsyon an, ou konpile li nan jenere dosye a pwogramasyon (.SOF oswa .pof) espesyalman pou aparèy la EP2S60F672C4.Pwosesis la konpilasyon tcheke pou distribisyon, devwa PIN, ak itilizasyon resous asire ke konsepsyon ou adapte nan achitekti FPGA a.Yon fwa konpile, bitstream ou a pare pou konfigirasyon aparèy.

Etap 2: Mete kanpe pyès ki nan konpitè pwogramasyon an

Next, ou prepare koòdone nan pwogramasyon fizik ant PC ou ak tablo a FPGA.Tipikman, sa a enplike nan konekte yon USB-Blaster oswa konpatib kab JTAG nan pò JTAG aparèy la.Ou ta dwe verifye ke Quartus II rekonèt pwogramè a ak ki se aparèy la sib kòrèkteman detekte.Etap sa a asire kominikasyon ki estab anvan ou kòmanse pwosesis konfigirasyon an.

Etap 3: Chaje dosye pwogramasyon an nan aparèy la

Sèvi ak zouti nan pwogramè Quartus II, ou ajoute konpile.Lè sa a, ou kòmanse sekans nan pwogramasyon, pandan ki se Bitstream a transfere ak chaje nan selil konfigirasyon SRAM FPGA a.Ou ta dwe kontwole ba a pwogrè ak mesaj estati konfime yon konfigirasyon siksè.Yon fwa konplè, FPGA a kòmanse egzekite lojik la pwograme imedyatman.

Etap 4: Verifye konfigirasyon an ak operasyon an

Apre pwogramasyon an, ou verifye ke aparèy la ap fonksyone kòm gen entansyon.Quartus II bay yon opsyon verifikasyon yo tcheke konfigirasyon CRC a ak siyal estati, asire ke konsepsyon an chaje kòrèkteman.Ou kapab tou teste I/O fonksyon ou oswa kouri yon simulation fonksyonèl konfime konpòtman sistèm lan.Etap final sa a asire konsepsyon ou se konplètman operasyonèl ak ki estab sou pyès ki nan konpitè.

EP2S60F672C4 avantaj ak dezavantaj

Avantaj

• Gwo dansite lojik pou desen konplèks

• Bon rapò pèfòmans-a-pri

• migrasyon fasil nan menm fanmi an

• Zouti devlopman ki estab ak matirite

• Pwouve fyab nan itilizasyon endistriyèl

Dezavantaj

• demode ak pi rèd sous

• Pi wo konsomasyon pouvwa pase plus FPGAs

• Pa gen resèpteur modèn gwo vitès

• Fèmti distribisyon pi difisil nan itilizasyon segondè

• Limite évolutivité pou pwotokòl nan lavni

EP2S60F672C4 Dimansyon anbalaj

|

Lèt |

Paramèt |

|

Kalite pake |

672-FBGA (Fineline BGA) |

|

Gwosè kò (L × W) |

27.00 mm × 27.00 mm |

|

Total pake wotè (a) |

Max 3.50 mm |

|

Wotè kanpe (A1) |

Min 0.30 mm |

|

Epesè substrate (a2) |

Max 3.00 mm |

|

Dyamèt boul (b) |

0.50 mm - 0.70 mm |

|

Boul boul (e) |

1.00 mm |

|

Kantite voye boul |

672 |

|

Style monte |

Sifas mòn |

|

Deskripsyon pake |

FBGA, 27 × 27 mm griy |

EP2S60F672C4 manifakti

EP2S60F672C4 FPGA a manifaktire pa Altera Corporation, yon pyonye dirijan nan aparèy lojik pwogramasyon.Nan 2015, Altera te rann pa Intel, ak pwodwi a kounye a tonbe anba Intel a pwogramasyon solisyon gwoup (PSG), ki kontinye ap sipòte ak ekipman pou Altera a etabli fanmi FPGA.Intel kenbe liy lan Stratix II kòm yon pati nan dosye pwodwi eritaj li yo, asire dokiman, sipò zouti, ak disponiblite alontèm pou aplikasyon pou endistriyèl ak kominikasyon.

Konklizyon

EP2S60F672C4 la konbine dansite lojik segondè, achitekti memwa fleksib, ak gaya I/O karakteristik sipòte konplèks sistèm dijital.Konsepsyon ALM ki baze sou li yo, memwa Trimatrix ™, blòk DSP, ak karakteristik jesyon revèy pèmèt aplikasyon efikas nan aplikasyon pou mande.Pandan ke li ofri fyab pwouve ak sipò devlopman ki gen matirite, li fè fas a limit tankou obsolesans ak mank de resèpteur modèn konpare ak plus jenerasyon FPGA.An jeneral, pèfòmans balanse li yo ak adaptabilite fè li yon chwa solid pou pwosesis siyal, kominikasyon, manyen done, ak aplikasyon pou prototip.

Fich pdf

EP2S60F672C4 Fèycheets:

Sou nou

ALLELCO LIMITED

Li piplis

Quick Inquiry

Tanpri voye yon ankèt, nou pral reponn imedyatman.

Kesyon yo poze souvan [FAQ]

1. Èske EP2S60F672C4 travay ak interfaces modèn memwa DDR?

Wi, li sipòte DDR, DDR2, QDR II, ak RLDRAM II interfaces, ki kouvri anpil komen estanda memwa ekstèn.Sa fè li apwopriye pou aplikasyon pou pwosesis done wo-bandwidth.

2. EP2S60F672C4 mande pou manyen espesyal oswa depo?

Wi, tankou lòt konpozan BGA-pake, li ta dwe estoke nan imidite-kontwole anbalaj ak okipe ak pwoteksyon ESD.Apre pratik depo apwopriye ede kenbe soldibilite ak fyab aparèy pandan asanble.

3. Ki jan ou ka diminye konsomasyon pouvwa nan EP2S60F672C4 Designs?

Ou ka optimize itilizasyon lojik, pòtay revèy rès, pi ba I/O tension kote sa posib, ak ogmante opsyon sentèz pouvwa-okouran nan Quartus II pou misyon pou minimize trase pouvwa an jeneral.

4. Ki zouti pwogramasyon ki nesesè pou EP2S60F672C4?

Ou pral bezwen Intel Quartus II lojisyèl pou konsepsyon, konpilasyon, ak pwogramasyon, ansanm ak yon USB-Blaster oswa konpatib kab JTAG konfigirasyon aparèy la.

5. Èske EP2S60F672C4 Sipò nan-Field Updates oswa Remote rkonfigurasyon?

Wi, li sipòte AES ki baze sou Bitstream chifreman ak aleka rkonfigurasyon, ki pèmèt ou mete ajou sistèm ou an byen san yo pa ranplase fizikman FPGA la.

Tout bagay sou LFXP6C-3FN256C Lattice Semiconductor

sou 2025/10/6

XC2C256-7TQ144C CPLD: pinout, karakteristik, pwogramasyon ak gid fich

sou 2025/10/3

Posts popilè

-

Enstriksyon konplèks Set Odinatè: Ki jan yo chanje informatique?

sou 8000/04/19 147780

-

USB-C pinout ak karakteristik

sou 2000/04/19 112050

-

Sèvi ak Xilinx Inifye Simulation Primitif: Yon Gid konplè nan FPGA Design ak Simulation

sou 1600/04/19 111352

-

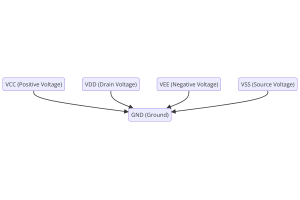

Tansyon ekipman pou pouvwa nan elektwonik: siyifikasyon VCC, VDD, VEE, VSS, ak GND

sou 0400/04/19 83806

-

RJ45 Connector Gid: Pinout, fil elektrik, Kalite Kab, ak Itilizasyon

sou 1970/01/1 79608

-

Gid la ultim nan kòd koulè fil nan sistèm elektrik modèn

Fason sistèm elektrik nou yo itilize koulè yo pa sèlman pou sanble.Chak koulè fil kounye a endike yon fonksyon espesifik, fè li pi fasil yo idantifye ak okipe konpozan elektrik kòrèkteman pandan en...sou 1970/01/1 66991

-

Purge Valv Gid: Fonksyon, sentòm, tès, ak ranplasman pou pèfòmans motè optimal

Valv la weteur se yon pati enpòtan nan sistèm yon machin nan ki ede kenbe lè a pwòp pa jere vapè gaz yo anvan yo ka chape anba nan atmosfè a.Sa a pa sèlman ede anviwònman an pa diminye polisyon, me...sou 1970/01/1 63113

-

Kalite (q) Faktè: Ekwasyon ak aplikasyon

Faktè bon jan kalite a, oswa 'Q', se enpòtan lè tcheke ki jan byen endukteur ak rezonan travay nan sistèm elektwonik ki itilize frekans radyo (RF).'Q' mezire ki jan byen yon sikwi minimize pèt enèj...sou 1970/01/1 63050

-

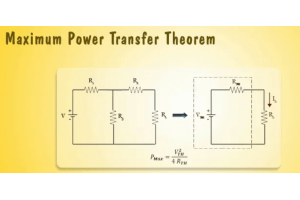

Atenn pèfòmans pik ak teyorèm nan transfè pouvwa maksimòm

Teyorèm maksimòm transfè pouvwa a eksplike kijan enèji ki sòti nan yon sous, tankou yon batri oswa dèlko, ap koule nan yon chaj ki konekte.Li montre kondisyon an egzak kote chaj la resevwa pouvwa k...sou 1970/01/1 54097

-

Espesifikasyon batri A23 ak konpatibilite

Batri a A23 se yon ti, silenn ki gen fòm batri ak vòltaj segondè.Yo te rele tou 23a, 23AE, oswa MN21, li kouri nan 12 vòlt ak pi wo pase AA oswa AAA pil.Konsepsyon espesyal li fè li pafè p...sou 1970/01/1 52199