XC2C256-7TQ144C CPLD: pinout, karakteristik, pwogramasyon ak gid fich

Nan gid sa a, ou pral jwenn yon gade klè nan XC2C256-7TQ144C a, yon ba-pouvwa CPLD soti nan Xilinx a CoolRunner-II fanmi (kounye a AMD).Ou pral aprann sou konfigirasyon PIN li yo, modèl CAD, ak karakteristik prensipal tankou kapasite lojik, I/O opsyon, sipò vòltaj, ak pouvwa-ekonomize fonksyon.Nou pral tou mache nan achitekti li yo, mwen/V koub, ak espesifikasyon, ki te swiv pa aplikasyon pou, pati menm jan an, etap pwogramasyon, avantaj ak dezavantaj, detay anbalaj, ak enfòmasyon manifakti pou ou ka konprann egzakteman ki jan aparèy sa a adapte nan pwojè ou yo.Katalòg

Ki sa ki XC2C256-7TQ144C a?

A XC2C256-7TQ144C se yon CPLD ba-pouvwa (konplèks aparèy lojik pwogramasyon) soti nan Xilinx a CoolRunner-II fanmi, kounye a yon pati nan AMD.Li prezante 256 macrocells ak vini nan yon pake 144-PIN TQFP, ki fèt pou vit, operasyon detèmine ak konsomasyon pouvwa minim.Opere sou yon nwayo 1.8 V, li ofri pèfòmans serye nan yon faktè fòm kontra enfòmèl ant epi li se byen adapte pou desen ki mande enstantane-sou kapasite ak aplikasyon lojik efikas.Kòm yon pati nan seri a versatile Coolrunner-II, li benefisye de yon achitekti pwouve ak konpatibilite konsepsyon gwo.

Kap chèche XC2C256-7TQ144C?Kontakte nou yo tcheke stock aktyèl, tan plon, ak prix.

XC2C256-7TQ144C PIN-OUT DIAGRAM

XC2C256-7TQ144C PIN-soti dyagram lan montre ki jan 144 broch yo ranje pou pouvwa, tè, JTAG, ak itilizatè-pwogramasyon I/O fonksyon.Pifò broch yo se mwen/O, ki ka configuré kòm entrain oswa rezilta, epi yo respire distribiye nan sipòte routage fleksib.VCC, VCCIO1, VCCIO2, Vaux, ak GND broch yo mete alantou pake a bay distribisyon pouvwa ki estab ak plizyè opsyon vòltaj I/O.Broch yo JTAG (TDI, TDO, TMS, TCK) yo gwoupe ansanm pou fasil nan-sistèm pwogramasyon ak tès yo.

XC2C256-7TQ144C Modèl CAD

XC2C256-7TQ144C senbòl

XC2C256-7TQ144C anprint

XC2C256-7TQ144C 3D modèl

XC2C256-7TQ144C karakteristik

• Kalite aparèy ak fanmi

XC2C256-7TQ144C a se yon aparèy lojik konplèks pwogramasyon (CPLD) ki fè pati fanmi CoolRunner-II devlope pa Xilinx (kounye a AMD).Li fèt pou konsomasyon pouvwa ki ba pandan y ap kenbe vit, pèfòmans lojik determinist, fè li ideyal pou lojik kontwòl ak aplikasyon pou entèfas.

• Kapasite lojik

Aparèy sa a gen 256 macrocells, ki se resous yo lojik pwogramasyon nan CPLD la.Sa yo macrocells ka configuré aplike divès kalite konbinezon ak sekans fonksyon lojik, bay kapasite modere pou kontwòl, lojik lakòl, ak interfaces otobis yo.

• Blòk lojik (blòk fonksyon)

Li entegre 16 blòk fonksyon ki òganize ak jere gwoup nan macrocells.Chak blòk bay lokal konekte ak pwodwi-tèm resous, sa ki pèmèt aplikasyon lojik fleksib ak routage efikas nan aparèy la.

• Itilizatè mwen/O broch

XC2C256-7TQ144C a ofri jiska 118 itilizatè-configurable I/O broch nan pake TQFP-144 li yo.Sa a konte PIN segondè pèmèt aparèy la koòdone ak subsistèm miltip ansanm, fè li apwopriye pou konplèks tablo-nivo desen.

• Nwayo vòltaj (VCC)

Nwayo a opere nan yon nominal 1.8 V (1.7 V a 1.9 V ranje), ki ede redwi konsomasyon pouvwa konpare ak ki pi gran 5 V cplds.Sa a vòltaj pi ba se itil nan modèn melanje-vòltaj sistèm dijital.

• Multi-Voltage I/O Sipò

Bank yo I/O sipòte plizyè estanda vòltaj ki gen ladan 1.5 V, 1.8 V, 2.5 V, ak 3.3 V. Fleksibilite sa a pèmèt CPLD a dirèkteman koòdone ak konpozan opere nan nivo vòltaj diferan san yo pa shifters nivo ekstèn.

• High-vitès operasyon

Avèk yon reta tipik PIN-a-PIN pwopagasyon nan alantou 5.7 ns (vitès klas "-7"), aparèy la delivre vit, pèfòmans detèmine.Sa fè li apwopriye pou aplikasyon pou distribisyon-kritik tankou adrès dekodaj, abitraj otobis, ak kontwòl.

• Ba konsomasyon pouvwa

Se seri a CoolRunner-II li te ye pou kouran ki ba anpil ki ba, souvan nan seri a microamp.Sa a pouvwa ki ba estatik, konbine avèk dinamik pouvwa-ekonomize karakteristik, pèmèt XC2C256-7TQ144C a yo dwe itilize efektivman nan batri ki mache ak oswa toujou-sou sistèm yo.

• Teknoloji Datagate

Karakteristik sa a pèmèt nan pòtay nan entrain rès, anpeche toggling nesesè ak diminye konsomasyon pouvwa dinamik.Li enpòtan nan aplikasyon kote sèten siyal yo inaktif pou peryòd ki long.

• Nan-sistèm jtag pwogramasyon

Aparèy la sipòte IEEE 1149.1 (JTAG) ak IEEE 1532 pou nan-sistèm pwogramasyon.Sa vle di CPLD a ka configuré, teste, ak reprogramasyon san yo pa retire li nan tablo a, senplifye devlopman ak dènye.

• Estrikti avanse revèy

XC2C256-7TQ144C gen ladan plizyè revèy mondyal, divizeur revèy, ak doub-kwen deklanche anrejistre.Li bay tou seri mondyal/Reyajiste ak lokal clocking pou chak macrocell, bay fleksib kontwòl sou distribisyon ak senkronizasyon.

• Entrain Schmitt-deklanche

Pins opinyon chwazi yo ka configuré kòm Schmitt deklannche amelyore iminite bri.Sa a se itil pou manyen ralanti oswa siyal opinyon bwi san yo pa ajoute ekstèn kondisyone sikwi.

• Karakteristik pwodiksyon fleksib

Rezilta yo sipòte operasyon twa eta a, kontwòl to touye, otobis-kenbe, ouvè-drenaj konfigirasyon, ak si ou vle rale-ups.Opsyon sa yo fè li fasil adapte CPLD a nan estanda otobis ak divès kalite kondisyon chaj ekstèn.

• Avanse matris entèrkonekte (AIM)

Yon avanse matris entèrkonèksyon avèk efikasite lyen blòk fonksyon, bay plen pwodwi-tèm routage atravè aparèy la.Sa a amelyore fleksibilite plasman lojik yo epi li ede kenbe previzib pèfòmans distribisyon.

Coolrunner-II Cpld Achitèk

Achitekti CPLD CoolRunner-II nan XC2C256-7TQ144C a bati alantou blòk fonksyon, blòk I/O, ak yon matris entèrkonèkte avanse (AIM).Chak blòk fonksyon gen macrocells ak yon etalaj lojik pwogramasyon (PLA) ki aplike itilizatè-defini lojik, pandan y ap bi a avèk efikasite wout siyal ant blòk.I/O bloke koòdone lojik entèn la ak broch ekstèn, ak dedye JTAG ak BSC/ISP sikwi sipò nan pwogramasyon sistèm ak tès yo.Sa a achitekti estriktire ak konekte pèmèt vit, pèfòmans detèmine ak konsomasyon pouvwa ki ba, fè li ideyal pou kontwòl, entèfas, ak lojik lakòl nan sistèm dijital.

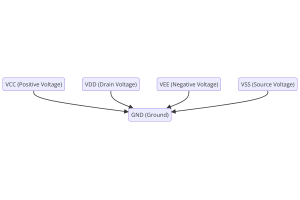

Tipik I/V koub pou XC2C256

Koub la tipik I/V pou XC2C256-7TQ144C a montre relasyon ki genyen ant pwodiksyon vòltaj (VO) ak pwodiksyon aktyèl (IO) pou diferan I/O tension ekipman pou (1.5 V, 1.8 V, 2.5 V, ak 3.3 V).Kòm vòltaj la ekipman pou ogmante, aparèy la ka sous oswa koule pi wo kouran anvan vòltaj la pwodiksyon kòmanse lage siyifikativman.Konpòtman sa a enpòtan pou konprann kapasite kondwi nan CPLD a lè entèfas ak eleman ekstèn, asire nivo siyal rete valab anba chaj.Anpil sèvi ak koub sa a yo chwazi apwopriye I/O tension ak asire operasyon serye nan aplikasyon pou ki mande espesifik aktyèl-kondwi fòs.

XC2C256-7TQ144C Espesifikasyon

|

Lèt |

Paramèt |

|

Fabrikan |

Am/xilinx |

|

Seri |

Coolrunner II |

|

Anbalaj |

Plato |

|

Estati pati |

Demode |

|

Kalite pwogramasyon |

Nan sistèm pwogramasyon |

|

Reta tan TPD (1) Max |

6.7 ns |

|

Pwovizyon pou vòltaj - Entèn |

1.7 V ~ 1.9 V |

|

Kantite eleman lojik/blòk |

16 |

|

Kantite macrocells |

256 |

|

Kantite pòtay |

6000 |

|

Kantite I/O |

118 |

|

Tanperati opere |

0 ° C ~ 70 ° C (TA) |

|

Kalite aliye |

Sifas mòn |

|

Pake / Ka |

144-LQFP

|

|

Pake aparèy founisè |

144-TQFP (20 × 20) |

|

Nimewo pwodwi baz |

XC2C256 |

XC2C256-7TQ144C Aplikasyon

1. Lakòl Lakòl ak koòdone Tranzisyon

XC2C256-7TQ144C a se ideyal pou mete ann aplikasyon lojik lakòl, ki konekte ak kowòdone siyal ant diferan konpozan dijital.Li ka okipe fonksyon tankou adrès dekodaj, abitraj otobis, ak tradiksyon pwotokòl, pèmèt kominikasyon lis ant mikrokontroleur, memwa, detèktè, ak lòt periferik.Distribisyon previzib li yo ak vit PIN-a-PIN reta asire serye entèfas menm nan desen tablo konplèks.

2. aparèy ba-pouvwa ak batri ki fonksyone

Mèsi a vit li yo zewo pouvwa (FZP) teknoloji ak trè ba aktyèl ki sibstiti an, sa a CPLD se trè apwopriye pou pòtab ak batri ki mache ak pil elektwonik.Li ka rete mache kontinyèlman pandan y ap konsome enèji minim, fè li pafè pou toujou-sou kontwòl oswa siveyans sikwi.Ou ka diminye itilizasyon pouvwa plis ak karakteristik tankou datagate, ki minimize dinamik oblije chanje lè entrain yo inaktif.

3. kontwòl lojik ak sekans

Aparèy la èksèl nan mete ann aplikasyon machin eta fini, kontwòl distribisyon, ak sekans siyal ki nesesè nan anpil sistèm entegre.Achitekti determinist, ki pa temèt li yo pèmèt lojik kontwòl la vin aktif imedyatman apre pouvwa-up san yo pa konfigirasyon reta.Sa fè li yon chwa fò pou lojik Reyajiste, sikwi handshaking, ak lòt travay kontwòl tan-kritik.

4. Sipò Sistèm Embedded ak lojik periferik

Nan desen entegre, XC2C256-7TQ144C a ka aji kòm yon chip sipò customizable, mete ann aplikasyon interfaces espesyalize oswa pwolonje kapasite yon mikrokontroleur la.Li ka okipe pwotokòl kominikasyon tankou SPI, I²C, oswa UART, jenere chip chwazi, oswa jere entèwonp routage.Pa debake fonksyon sa yo soti nan CPU a, li senplifye devlopman firmwèr ak amelyore pèfòmans sistèm an jeneral.

Xc2c256-7tq144c pati ki sanble

|

Spesifikasyon |

XC2C256-7TQ144C |

XC2C256-7TQ144I |

Xc2c256-7tqg144i |

XC2C256-7VQ100C |

XC2C256-7VQG100C |

XC2C256-6TQ144C |

|

Aparèy fanmi |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

|

Dansite lojik (MacroCells) |

256 |

256 |

256 |

256 |

256 |

256 |

|

Kalite pake |

TQFP-144 |

TQFP-144 |

TQFP-144 (PB-gratis) |

VQFP-100 |

VQFP-100 (PB-gratis) |

TQFP-144 |

|

Vitès |

-7 |

-7 |

-7 |

-7 |

-7 |

-6 (pi vit) |

|

Range Tanperati |

Komèsyal (0 - 70 ° C) |

Endistriyèl (-40-85 ° C) |

Endistriyèl (-40-85 ° C) |

Komèsyal (0 - 70 ° C) |

Komèsyal (0 - 70 ° C) |

Komèsyal (0 - 70 ° C) |

|

Mwen/o konte PIN |

118 |

118 |

118 |

80 |

80 |

118 |

|

Nwayo vòltaj (VCC) |

1.8 V |

1.8 V |

1.8 V |

1.8 V |

1.8 V |

1.8 V |

|

I/O sipò vòltaj |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

|

Konfòmite / PB-gratis |

Estanda |

Estanda |

PB-gratis / ROHS |

Estanda |

PB-gratis / ROHS |

Estanda |

|

Diferans |

Vèsyon debaz komèsyal yo |

Version Endistriyèl Tanpèt |

Endistriyèl + PB-gratis vèsyon |

Pi piti pake, mwens mwen/o |

PB-gratis vèsyon ki pi piti |

Pi vit vèsyon distribisyon |

XC2C256-7TQ144C etap pwogramasyon

Pwogramasyon XC2C256-7TQ144C a se yon pwosesis senp ki enplike nan prepare konsepsyon ou, génération dosye a pwogramasyon, ak loading li nan CPLD a nan JTAG.Pa swiv chak etap ak anpil atansyon, ou ka asire yon konfigirasyon siksè ak operasyon aparèy apwopriye sou tablo ou an.

1. Design ak sentèz

Ou kòmanse pa ekri konsepsyon lojik ou lè l sèvi avèk HDL (VHDL oswa Verilog) oswa antre schematic.Apre w fin ranpli konsepsyon an, ou kouri pwosesis la sentèz, ki konvèti lojik ou nan estrikti entèn aparèy la nan macrocells ak konekte.Etap sa a asire konsepsyon ou se konpatib ak achitekti a XC2C256 ak pare pou aplikasyon.

2. Place & Route / Aplikasyon (Fitting)

Apre sa, ou fè kote ak wout, ke yo rele tou Fitting, ki asiyen lojik sentetiz ou a aktyèl macrocells fizik ak resous routage andedan CPLD la.Zouti a tcheke kontrent distribisyon, rezoud itilizasyon resous, ak optimize chemen yo satisfè pèfòmans nan konsepsyon ou.Sa a asire kous la pral kouri fiable yon fwa pwograme nan aparèy la.

3. jenere dosye pwogramasyon

Yon fwa aplikasyon an se konplè, ou jenere dosye a pwogramasyon (ti jan, konfiti, oswa fòma SVF) ki gen done yo konfigirasyon egzak pou aparèy la.Dosye sa a reprezante ki jan chak MacroCell, konekte, ak I/O se mete kanpe aplike lojik ou.Èske w gen sa a dosye pare ki nesesè anvan ou deplase sou pwogram nan aparèy aktyèl.

4. JTAG / In-System Programming

Finalman, ou konekte aparèy la nan PC ou lè l sèvi avèk yon kab pwogram JTAG ak louvri zouti nan enpak xilinx (oswa ekivalan).Lè sa a, ou chaje dosye a pwogramasyon pwodwi ak telechaje li nan XC2C256-7TQ144C a nan broch yo JTAG (TDI, TDO, TCK, TMS).Yon fwa pwosesis la konplè, CPLD a imedyatman kòmanse opere ak lojik pwograme ou, san yo pa egzije yon sik pouvwa oswa memwa konfigirasyon ekstèn.

Xc2c256-7tq144c avantaj ak dezavantaj

Avantaj

• Pouvwa ki ba anpil, ideyal pou desen ki mache ak batri.

• Instant-sou operasyon ki pa gen okenn reta konfigirasyon.

• Distribisyon previzib pou fèmen konsepsyon pi fasil.

• Ranplase miltip bato lojik disrè, ekonomize espas ak pri.

• Sipòte plizyè tension I/O san yo pa shifters nivo ekstèn.

Dezavantaj

• Limite kapasite lojik konpare ak pi gwo cplds oswa FPGAs.

• Pa gen bati-an DSP, RAM, oswa resèpteur gwo vitès.

• Vin demode, fè nan lavni apwovizyone pi rèd.

• Pi ba plafon pèfòmans pou aplikasyon pou gwo vitès.

• Fleksibilite mwens routage pou desen konplèks oswa iregilye.

Xc2c256-7tq144c dimansyon anbalaj

|

Lèt |

Paramèt |

|

Kalite pake |

TQFP-144 |

|

Pake gwosè kò |

20 mm × 20 mm |

|

Anplasman plon |

0.5 mm |

|

Kantite broch |

144 |

|

Pake wotè (max) |

1.4 mm |

|

Pake epesè (nominal) |

1.0 mm |

|

Plon longè |

0.45 mm ~ 0.75 mm |

|

Plon lajè |

0.17 mm ~ 0.27 mm |

|

Kalite aliye |

Sifas mòn |

|

Pake aparèy founisè |

144-TQFP (20 × 20) |

XC2C256-7TQ144C manifakti

XC2C256-7TQ144C a manifaktire pa Xilinx, yon konpayi dirijan nan solisyon lojik pwogramasyon.Xilinx se lajman rekonèt pou pyonye FPGA ak CPLD teknoloji, bay aparèy serye ak pèfòmans-wo pou endistriyèl, komèsyal, ak aplikasyon pou konsomatè yo.Jodi a, Xilinx opere kòm yon pati nan AMD, kontinye delivre avanse pwodwi lojik pwogramasyon ak fò sipò alontèm ak inovasyon.

Konklizyon

XC2C256-7TQ144C a vle di soti pou konsomasyon pouvwa ki ba li yo, vit pèfòmans detèmine, ak milti-vòltaj I/O fleksibilite, fè li yon chwa serye pou desen modèn dijital.Konbinezon balanse li yo nan 256 macrocells, 118 I/O broch, ak avanse achitekti entèrkonèksyon sipòte nan yon pakèt domèn kontwòl, entèfas, ak lakòl fonksyon lojik.Avèk sipò pou pwogram nan-sistèm, datagate pouvwa-ekonomize karakteristik, ak gaya I/O konfigirasyon, li entegre fèt san pwoblèm nan sistèm entegre ak anviwònman melanje-vòltaj.

Fich pdf

XC2C256-7TQ144C FACASHEETS:

Sou nou

ALLELCO LIMITED

Li piplis

Quick Inquiry

Tanpri voye yon ankèt, nou pral reponn imedyatman.

Kesyon yo poze souvan [FAQ]

1. Èske XC2C256-7TQ144C a mande pou memwa konfigirasyon ekstèn?

No youn nan avantaj li yo se enstantane-sou operasyon.Se konfigirasyon an ki estoke intern, se konsa li pouvwa moute pare yo kouri san yo pa nenpòt ki bal ekstèn oswa memwa flash.

2. Ki zouti pwogramasyon ki konpatib ak XC2C256-7TQ144C?

Ou ka pwogram aparèy la lè l sèvi avèk lojisyèl enpak xilinx ak yon kab pwogram JTAG.Anpil tou itilize konpatib pwogramasyon JTAG twazyèm pati, men asire w ke yo sipòte IEEE 1149.1/1532 estanda.

3. Èske XC2C256-7TQ144C a ranplase plizyè lojik disrè ICS nan konsepsyon ou a?

Wi.Avèk 256 macrocells li yo ak fleksib I/O, sa a CPLD ka entegre plizyè lojik lakòl ak fonksyon kontwòl nan yon sèl aparèy, ede ou diminye espas tablo ak konte eleman.

4. Èske XC2C256-7TQ144C a apwopriye pou aplikasyon pou batri ba-pouvwa?

Wi.Mèsi a vit li yo zewo pouvwa (FZP) teknoloji ak trè ba ki sibstiti aktyèl, li la ideyal pou toujou-sou sikui, aparèy pòtab, ak pouvwa-sansib sistèm entegre.

5. Èske ou ka itilize XC2C256-7TQ144C a pou pwosesis siyal segondè-vitès?

Li pa fèt pou gwo vitès DSP oswa travay émetteur.Pandan ke li delivre vit PIN-a-PIN reta, li la pi byen adapte pou kontwòl, entèfas, ak lojik distribisyon, pa konplèks pwosesis done.

EP2S60F672C4 FPGA: Karakteristik, Aplikasyon, Pwogramasyon & Fèy Gid

sou 2025/10/4

EPM3256AFC256-7 CPLD Apèsi sou lekòl la: Karakteristik, pinout, pwogramasyon ak aplikasyon pou

sou 2025/10/3

Posts popilè

-

Enstriksyon konplèks Set Odinatè: Ki jan yo chanje informatique?

sou 8000/04/18 147776

-

USB-C pinout ak karakteristik

sou 2000/04/18 112018

-

Sèvi ak Xilinx Inifye Simulation Primitif: Yon Gid konplè nan FPGA Design ak Simulation

sou 1600/04/18 111351

-

Tansyon ekipman pou pouvwa nan elektwonik: siyifikasyon VCC, VDD, VEE, VSS, ak GND

sou 0400/04/18 83775

-

RJ45 Connector Gid: Pinout, fil elektrik, Kalite Kab, ak Itilizasyon

sou 1970/01/1 79571

-

Gid la ultim nan kòd koulè fil nan sistèm elektrik modèn

Fason sistèm elektrik nou yo itilize koulè yo pa sèlman pou sanble.Chak koulè fil kounye a endike yon fonksyon espesifik, fè li pi fasil yo idantifye ak okipe konpozan elektrik kòrèkteman pandan en...sou 1970/01/1 66962

-

Purge Valv Gid: Fonksyon, sentòm, tès, ak ranplasman pou pèfòmans motè optimal

Valv la weteur se yon pati enpòtan nan sistèm yon machin nan ki ede kenbe lè a pwòp pa jere vapè gaz yo anvan yo ka chape anba nan atmosfè a.Sa a pa sèlman ede anviwònman an pa diminye polisyon, me...sou 1970/01/1 63104

-

Kalite (q) Faktè: Ekwasyon ak aplikasyon

Faktè bon jan kalite a, oswa 'Q', se enpòtan lè tcheke ki jan byen endukteur ak rezonan travay nan sistèm elektwonik ki itilize frekans radyo (RF).'Q' mezire ki jan byen yon sikwi minimize pèt enèj...sou 1970/01/1 63041

-

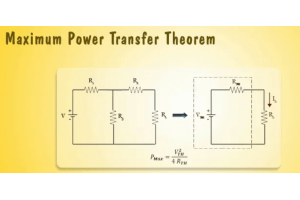

Atenn pèfòmans pik ak teyorèm nan transfè pouvwa maksimòm

Teyorèm maksimòm transfè pouvwa a eksplike kijan enèji ki sòti nan yon sous, tankou yon batri oswa dèlko, ap koule nan yon chaj ki konekte.Li montre kondisyon an egzak kote chaj la resevwa pouvwa k...sou 1970/01/1 54097

-

Espesifikasyon batri A23 ak konpatibilite

Batri a A23 se yon ti, silenn ki gen fòm batri ak vòltaj segondè.Yo te rele tou 23a, 23AE, oswa MN21, li kouri nan 12 vòlt ak pi wo pase AA oswa AAA pil.Konsepsyon espesyal li fè li pafè p...sou 1970/01/1 52186