XCV200-6FG456C FPGA: Karakteristik, espesifikasyon, pwogramasyon, ak aplikasyon pou

XCV200-6FG456C a se yon FPGA pwisan (jaden-pwogramasyon etalaj pòtay) soti nan AMD Xilinx Virtex ® seri a.Gid sa a eksplike karakteristik li yo, Layout PIN, etap pwogramasyon, ak itilizasyon.Avèk gwo pouvwa pwosesis, opsyon konsepsyon fleksib, ak fò opinyon/pwodiksyon (I/O) kapasite, sa a FPGA ede bati vit ak serye sistèm dijital.Si ou ap travay sou rezo, sistèm kontwòl, oswa elektwonik koutim, gid sa a ap ede ou konprann ki jan ka XCV200-6FG456C a dwe itilize nan pwojè ou a.Katalòg

XCV200-6FG456C Apèsi sou lekòl la

A XCV200-6FG456C se yon modèl remakab nan fanmi AMD Xilinx Virtex® FPGA, ki fèt pou bay solisyon lojik gaya pwogramasyon pou sistèm dijital konplèks.Sa a chip espesifik englobe apeprè 236,666 pòtay sistèm ak karakteristik 1,176 blòk lojik configurable (CLBs) ak 5,292 selil lojik.Li gen ladan tou 57,344 Total RAM Bits ak sipòte 284 I/O broch, loje nan yon 456-boul amann-pitch boul etalaj boul (FBGA) pake, mezire 23mm x 23mm.Modèl sa a opere sou yon vòltaj nominal 2.5V, ak yon seri de 2.375V 2.625V, epi yo ka fonksyone nan yon seri tanperati 0 ° C a 85 ° C.Seri a pi laj Virtex® akeyir nan yon seri de aplikasyon pou ak dansite soti nan 50,000 a plis pase 1 milyon pòtay sistèm ak pousantaj revèy sistèm ki rive jiska 200 megaèrts.Li sipòte anpil I/O estanda ki gen ladan LVTTL, LVCMOS, ak PCI, nan mitan lòt moun.Karakteristik tankou reta-fèmen pasan (DLLs), configurable blòk lojik ak entegre memwa, ak dedye pote lojik pou operasyon aritmetik amelyore fonctionnalités li yo.Manifaktire lè l sèvi avèk yon 0.22 µm 5-kouch pwosesis metal, Virtex ® fanmi an garanti pèfòmans ak disponiblite.

Si ou ap chèche entegre tèt-niveau teknoloji FPGA nan pwodwi ou oswa sistèm, achte XCV200-6FG456C a nan esansyèl avèk nou se yon mouvman entelijan.Li satisfè estanda endistri yo ak kenbe ou devan yo nan bezwen teknoloji nan lavni.

XCV200-6FG456C Karakteristik

• Sistèm pòtay: XCV200-6FG456C a ofri apeprè 236,666 pòtay sistèm lan.Sa a konte pòtay segondè pèmèt pou aplikasyon an nan konplèks entegre sikwi lojik dijital sou yon chip sèl, amelyore tou de pèfòmans ak adaptabilite nan yon seri de aplikasyon pou.

• Resous lojik: Li gen ladan 1,176 blòk lojik configurable (CLBs) ak 5,292 selil lojik.Resous sa yo bon pou konsepsyon sikwi dijital fleksib ak évolutive.CLBs ka pwograme fè yon gran varyete fonksyon ki lojik, pandan y ap gwo kantite selil lojik pèmèt manyen nan operasyon lojik vaste ak pwosesis.

• Memwa: Aparèy la bay 57,344 Bits nan RAM, distribye nan mitan blòk lojik li yo.Sa a se RAM entegre itilize pou aplikasyon pou ki mande pou vit ak efikas depo done ak Rekipere, sipòte gwo vitès operasyon done entegral nan sistèm modèn dijital.

• I/O kapasite: Avèk 284 broch opinyon/pwodiksyon, XCV200-6FG456C a fasilite kapasite entèfas vaste.Sa yo I/O broch sipòte divès kalite estanda siyal ak pèmèt FPGA a yo kominike efektivman ak lòt konpozan nan yon sistèm, tankou aparèy memwa, processeurs, ak periferik.

• Vòltaj ak tanperati ranje: Opere nan yon vòltaj nominal nan 2.5V, ak yon seri akseptab soti nan 2.375V 2.625V, sa a FPGA ki fèt pou ba-pouvwa konsomasyon pandan w ap kenbe pèfòmans gaya.Li ka opere nan yon seri tanperati junction de 0 ° C a 85 ° C, asire disponiblite anba divès kondisyon anviwònman an.

XCV200-6FG456C Dyagram fonksyon PIN

A XCV200-6FG456C Dyagram fonksyon PIN se yon reprezantasyon estriktire nan devwa PIN FPGA a, kategori nan bank diferan (Bank 0 a Bank 7).Chak gwoup bank broch ki baze sou fonksyon yo ak plasman fizik sou pake a FPGA.Sistèm nimewote ak etikèt la swiv yon modèl kadriyaj kote ranje yo deziye pa lèt (a, b, c, elatriye), ak kolòn pa nimewo (1, 2, 3, elatriye), ki fasilite idantifikasyon rapid nan broch espesifik.Bank sa yo koresponn ak diferan fonksyon opinyon/pwodiksyon, pouvwa, tè, ak dedye routage siyal.Pins yo asiyen divès kalite gwoupman fonksyonèl, ki gen ladan jeneral-bi I/O (GPIO), souvan ki make kòm "G" (Jeneral Antre/Sòti), "V" (ekipman pou vòltaj), ak "O" (pwodiksyon).Pouvwa ak broch tè yo make klèman, asire ki estab operasyon FPGA.Pins espesyal-bi tankou entrain revèy, retabli, ak siyal kontwòl yo idantifye ak senbòl tankou "R" oswa "T."Gen kèk broch tou sèvi wòl dedye kominikasyon, ki gen ladan konfigirasyon JTAG ak segondè-vitès clocking, pou pwogramasyon ak debogaj.

XCV200-6FG456C Dyagram blòk

Antre/Sòti blòk

Dyagram lan reprezante Antre/Sòti blòk (IOB) Estrikti nan XCV200-6FG456C FPGA a, ki se yon manm nan fanmi an Virtex Xilinx.Dyagram lan montre eleman kle ki enplike nan operasyon opinyon ak pwodiksyon, en koule done yo ak mekanis kontwòl.Nan nwayo a nan dyagram lan, twa D baskile-flops yo te itilize yo enskri siyal pou opinyon, pwodiksyon, ak tri-eta kontwòl.Se enskri nan pwodiksyon kontwole pa OCE a (pwodiksyon revèy pèmèt) siyal, ki detèmine lè se done yo pwodiksyon fèmen.Menm jan tou, se enskri nan tri-eta kontwole pa TCE a (Tri-eta revèy pèmèt), pèmèt oswa enfimite tanpon an pwodiksyon.Rejis la opinyon kaptire done fèk ap rantre ak aplike yon reta pwogramasyon anvan pase li nan lojik la FPGA entèn nan IBUF a (tanpon opinyon).OBUFT a (Tri-eta pwodiksyon tanpon) asire ke FPGA a ka swa kondwi yon siyal sou pad la (I/O PIN) oswa mete l 'nan yon eta-wo enpedans, tou depann de lojik la kontwòl.Yon sikwi gadò fèb enkli sou pad la yo kenbe dènye eta a lojik li te ye lè pa gen okenn chofè aktif ki prezan, anpeche kondisyon entansyonel k ap flote.Vòltaj referans lan (VREF) yo itilize pou sèten estanda opinyon, tankou SSTL oswa HSTL, ki mande pou nivo vòltaj egzak pou operasyon apwopriye.An jeneral, estrikti sa a IOB pèmèt FPGA a jere gwo vitès transmisyon done, sipòte diferan I/O estanda, epi yo bay kontwòl fleksib sou distribisyon siyal ak entegrite.

Mèt/esklav mòd seri

A Mèt/esklav mòd seri Dyagram blòk montre pwosesis konfigirasyon yon FPGA Virtex, espesyalman XCV200-6FG456C a, lè yo pwograme nan yon konfigirasyon Daisy-Chain lè l sèvi avèk yon EEPROM seri (XC1701L).Nan konfigirasyon sa a, yon sèl aparèy Virtex opere kòm mèt la, kontwole revèy la konfigirasyon (CCLK) ak seri done konfigirasyon transmèt nan plis FPGA esklav nan chèn lan.Mèt la FPGA inisye pwosesis la konfigirasyon pa revandike siyal la pwogram, retabli tout aparèy nan chèn lan.Yon fwa inisyalizasyon konplè, siyal la init endike preparasyon pou, ak konfigirasyon done ap koule soti nan seri a EEPROM (XC1701L) nan DIN la (done nan) PIN nan FPGA a mèt.Mèt la FPGA li done ki sòti nan EEPROM a ak transmet li nan DOUT (done soti) nan ki vin apre esklav FPGAs, senkronize transfè done lè l sèvi avèk siyal la CCLK.Se siyal la fè itilize yo endike konfigirasyon siksè, ak yon si ou vle rale-up rezisteur asire yon eta ki estab segondè lè konfigirasyon se konplè.EEPROM XC1701L la kontwole pa mèt FPGA a lè l sèvi avèk CLK, done, CE (ChIP pèmèt), ak Reyajiste/OE (pwodiksyon pèmèt) siyal, asire ke done yo konfigirasyon ki estoke kòrèkteman rekipere.Metòd konfigirasyon sa a efikas pou pwogram FPGA miltip lè l sèvi avèk yon EEPROM sèl, diminye konpleksite fil elektrik ekstèn ak asire tout aparèy resevwa done konfigirasyon senkronize.

XCV200-6FG456C Espesifikasyon

|

Lèt |

Paramèt |

|

Fabrikan |

Amd xilinx

|

|

Seri |

Virtex® |

|

Anbalaj |

Plato |

|

Estati pati |

Demode |

|

Kantite laboratwa/CLBS |

1176 |

|

Kantite eleman lojik/selil |

5292 |

|

Total Bits Ram |

57344 |

|

Kantite I/O |

284 |

|

Kantite pòtay |

236666 |

|

Vòltaj - Pwovizyon pou |

2.375V ~ 2.625V |

|

Kalite aliye |

Sifas mòn |

|

Tanperati opere |

0 ° C ~ 85 ° C (TJ) |

|

Pake / Ka |

456-BBGA |

|

Pake aparèy founisè |

456-FBGA (23x23) |

|

Nimewo pwodwi baz |

XCV200 |

XCV200-6FG456C Aplikasyon

Telekominikasyon ak rezo

XCV200-6FG456C a èksèl nan telekominikasyon ak aplikasyon pou rezo akòz kapasite li nan okipe transmisyon done gwo vitès ak travay pwosesis konplèks siyal.Konte pòtay segondè li yo ak gaya I/O kapasite pèmèt li sipòte fonksyon tankou pwosesis pake, batman siyal/demodulasyon, ak pwotokòl koreksyon erè.

Pwosesis siyal dijital (DSP)

Ideyal pou aplikasyon pou DSP, sa a FPGA ka fè rapid ak konplèks kalkil matematik ki nesesè nan teknoloji odyo ak pwosesis videyo.Si li nan pou sistèm miltimedya, rekonesans vwa, oswa sèvis difizyon, kapasite nan pwosesis XCV200-6FG456C a pwosesis ak entegre memwa sipò efikas ak bon jan kalite pwosesis siyal.

Sistèm kontwòl endistriyèl

Nan automatisation endistriyèl la, XCV200-6FG456C a bay pèfòmans ki nesesè yo jere sistèm kontwòl ak rezo automatisation.Kapasite li nan egzekite travay kontwòl miltip ansanm pandan y ap asire fwa repons fè li apwopriye pou aplikasyon pou nan kontwòl pwosesis, robotic, ak vizyon machin.

Enstriman medikal

Presizyon FPGA a ak vitès yo se gwo nan D 'medikal ak ekipman dyagnostik, kote li ede nan pwosesis la nan algoritm konplèks pou aplikasyon pou D' tankou MRI, ultrason, ak analiz CT.Kapasite XCV200-6FG456C a asire ke li ka okipe debi done segondè ak pwosesis konplike ki nesesè nan teknoloji modèn medikal.

XCV200-6FG456C Pati ki sanble

XCV200-6FG456C etap pwogramasyon

Etap pwogramasyon pou XCV200-6FG456C a:

1. Design antre

Premye faz nan pwogram FPGA enplike nan defini lojik dijital la ak fonctionnalités nan sistèm ou an.Sa a ka fè lè l sèvi avèk Lang Deskripsyon Materyèl (HDLs) tankou VHDL oswa Verilog, kote ou ekri kòd ki espesifye ki jan FPGA a pwosesis done ak reyaji ak lòt pyès ki nan konpitè.Zouti antre schematic ki disponib nan lojisyèl konsepsyon FPGA tankou Xilinx ISE oswa Vivado ka itilize.Metòd sa a enplike nan kreye yon reprezantasyon vizyèl nan lojik la pa trenen ak jete konpozan, ki kèk jwenn plis entwisyon pase kòd ekri.

2. sentèz

Yon fwa konsepsyon an fini, pwochen etap la se sentèz, kote yon zouti tankou XST Xilinx a (Xilinx sentèz teknoloji) transfòme kòd HDL ou a oswa konsepsyon schematic nan yon netlist.Netlist sa a dekri kous la an tèm de jenerik eleman dijital, tankou pòtay lojik ak anrejistre.Pwosesis la sentèz tou enplike nan optimize konsepsyon an satisfè kondisyon pèfòmans ak minimize itilizasyon resous pou efikas operasyon FPGA.

3. Aplikasyon

Pwosesis aplikasyon an kòmanse ak tradiksyon, konbine konsepsyon ou a ak dosye contrainte ki presize paramèt tankou frekans revèy ak devwa PIN.Apre tradiksyon an, etap kat la asiyen eleman yo nan netlist ou a resous fizik espesifik sou FPGA a, tankou gade-up tab (LUTs) ak baskile-flops.Plasman an ak faz routage Lè sa a, detèmine kote fizik yo nan chak eleman nan achitekti FPGA a ak etabli koneksyon ki genyen ant yo nan resous konekte pwogramasyon.Etap sa a se gwo pou reyalize mesures yo pèfòmans vle, ki gen ladan frekans revèy.

4. Jenerasyon Bitstream

Apre plasman siksè ak routage, zouti a jenere yon Bitstream, yon dosye konfigirasyon binè ki gen tout enfòmasyon ki pwogramasyon pou FPGA la.Li se souvan rekòmande yo simulation konsepsyon final la post-plasman asire Bitstream a ap konpòte yo jan yo espere nan kondisyon yo.Etap verifikasyon sa a ede evite pwoblèm potansyèl pandan operasyon aktyèl la.

5. konfigirasyon

Etap final la enplike nan chaje Bitstream a nan FPGA a lè l sèvi avèk divès metòd konfigirasyon.Mòd la esklav-seri, yon opsyon ki senp ak pri-efikas, konfigirasyon FPGA a atravè yon aparèy mèt ekstèn ki voye done seri.Nan mòd mèt-seri, FPGA a otonòm li Bitstream a soti nan yon bal atache Seri.Pou konfigirasyon gwo vitès, mòd SelectMap pèmèt yon mikro ekstèn chaje done nan FPGA a byen vit.Anplis de sa, yo itilize mòd JTAG pa sèlman pou pwogramasyon, men tou pou fè tès ak debogaj, itilize yon koòdone estanda pou nan-sistèm pwogramasyon ak fwontyè-eskanè tès yo.

XCV200-6FG456C avantaj

Pèfòmans

Seri a Xilinx Virtex, ki ki XCV200-6FG456C a ki dwe, se optimisé pou pèfòmans segondè-vitès, ofri pousantaj revèy sistèm ki rive jiska 200 megaèrts.Sa fè li byen adapte pou aplikasyon ki mande pou pwosesis done vit, asire manyen efikas nan algoritm konplèks ak operasyon gwo vitès tankou telekominikasyon, pwosesis, ak miltimedya.

I/O Standards Sipò

FPGA sa a sipòte yon pakèt domèn estanda/pwodiksyon, ki gen ladan LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT, ak AGP.Estanda sa yo vaste I/O sipò pèmèt XCV200-6FG456C a entegre transparans ak divès kalite konpozan sistèm, amelyore sèvis piblik li yo atravè divès ekosistèm dijital.Fleksibilite sa a pèmèt yo adapte FPGA a nan diferan kondisyon entèfas san yo pa modifikasyon sistèm.

Jesyon revèy

XCV200-6FG456C a enkòpore plizyè reta-fèmen pasan (DLLs) pou distribisyon revèy ak jesyon nan sistèm lan.DLL sa yo ede nan amelyore distribisyon sistèm ak disponiblite pa bay siyal revèy egzak ki nesesè pou operasyon synchronous.Karakteristik sa a enpòtan nan diminye erè sistèm ak amelyore pèfòmans jeneral, patikilyèman nan desen konplèks ki mande egzat distribisyon ak senkronizasyon.

Konsepsyon fleksibilite

Avèk 1,176 blòk lojik configurable ak 5,292 selil lojik, XCV200-6FG456C a ofri resous lojik sibstansyèl ak kapasite a aplike yon seri divès nan fonksyonalite.Soti nan lojik lakòl senp nan konplike sistèm dijital, sa a FPGA sipòte kondisyon konsepsyon konplèks, fè li ideyal pou aplikasyon pou nan informatique koutim, pwosesis siyal dijital, ak prototip.

Pwototip rapid

FPGAs tankou XCV200-6FG456C a yo renome pou kapasite yo nan sipòte pwototip rapid.Aparèy sa a pèmèt pou iterasyon konsepsyon rapid epi yo ka konfigure nan-jaden, ki se yon avantaj pou sik devlopman jan li diminye tan-a-mache.Li adapte tou avèk efikasite nan chanje kondisyon oswa dènye nan espesifikasyon pwojè, asire ke pwodwi final yo yo monte-a-dat ak dènye estanda yo teknolojik.

Kapasite entegrasyon

Kapasite yo entegrasyon nan XCV200-6FG456C a fasilite konsolidasyon an nan eleman miltip disrè nan yon chip sèl.Entegrasyon sa a ka mennen nan konpleksite sistèm redwi, pi ba konsomasyon pouvwa, ak ekonomi pri.Pa minimize kantite eleman separe ki nesesè, FPGA sa a senplifye pwosesis konsepsyon ak amelyore fyab la ak Compact nan sistèm la an jeneral.

XCV200-6FG456C Dimansyon anbalaj

XCV200-6FG456C a se yon jaden pòtay pwogramasyon pwogramasyon (FPGA) soti nan seri Virtex® AMD a, loje nan yon 456-boul amann-pitch boul etalaj etalaj (FBGA) pake.

• Kalite pake: 456-FBGA

• Gwosè pake: 23 mm x 23 mm

• Anplasman boul: 1.0 mm

XCV200-6FG456C manifakti

XCV200-6FG456C a se yon jaden pòtay pwogramasyon pwogramasyon (FPGA) orijinal devlope pa Xilinx, yon konpayi li te ye pou pèfòmans-wo li yo pwogramasyon aparèy lojik.Apre akizisyon Xilinx a pa AMD, XCV200-6FG456C a se kounye a ki asosye ak AMD kòm manifakti aktyèl li yo.Sepandan, modèl FPGA sa a demode e pa nan pwodiksyon.AMD kontinye sipòte plus Architectures FPGA ak pèfòmans ranfòse, efikasite pouvwa, ak lonjevite pwolonje, fè altènativ modèn pi preferab pou desen nouvo.

Konklizyon

XCV200-6FG456C a se yon FPGA versatile ak gwo vitès, itil pou aplikasyon pou teknoloji anpil.Pandan ke li pa te fè ankò, li se toujou yon bon chwa pou pi gran sistèm ki bezwen pèfòmans serye.Gid sa a te kouvri konsepsyon li yo, etap pwogramasyon, ak itilizasyon pratik, fè li pi fasil yo konprann ki jan li fonksyone ak ki jan li kapab itilize.Kòm plus FPGAs vin disponib, ou ka itilize konesans sa a yo chwazi FPGA a dwa pou bezwen ou yo ak amelyore desen dijital.

Fich pdf

XCV200-6FG456C fich:

Sou nou

ALLELCO LIMITED

Li piplis

Quick Inquiry

Tanpri voye yon ankèt, nou pral reponn imedyatman.

Kesyon yo poze souvan [FAQ]

1. Ki sa ki konsomasyon an pouvwa nan XCV200-6FG456C a?

XCV200-6FG456C a opere nan 2.5V, ak yon seri vòltaj nan 2.375V 2.625V.Konsomasyon pouvwa depann sou itilizasyon lojik ak frekans revèy, men kòm yon FPGA ki pi gran, li ka mwens pouvwa-efikas pase plus aparèy xilinx.Yo ta dwe konsidere bon jesyon pouvwa ak dissipation chalè.

2. Kijan XCV200-6FG456C a konpare ak XCV200-6FG256C a?

XCV200-6FG456C a gen yon pake pi gwo (456-boul FBGA) konpare ak XCV200-6FG256C a (256-boul FBGA), ofri plis I/O broch (284 vs. 172) ak potansyèlman pi bon pèfòmans pou aplikasyon pou ki mande anpil entèfas.Si konsepsyon ou depann sou plis I/O kapasite, XCV200-6FG456C a se chwa ki pi bon.

3. Èske mwen ka rprograme XCV200-6FG456C plizyè fwa?

Wi, XCV200-6FG456C a se yon SRAM ki baze sou FPGA, sa vle di li ka reprogramasyon yon nimewo san limit nan fwa osi lontan ke pouvwa apwovizyone.Sepandan, ou pral bezwen ekstèn ki pa temèt memwa (EEPROM oswa Flash) kenbe Bitstream a apre yon sik pouvwa.

4. Èske XCV200-6FG456C Sipò pou Kominikasyon Seri High-vitès la?

XCV200-6FG456C a sipòte plizyè estanda I/O tankou LVTTL, LVCMOS, PCI, GTL, HSTL, ak SSTL, men li pa te bati-an gwo vitès Serdes (Serializer/Deserializer) oswa resèpteur tankou FPGAs modèn.Pou aplikasyon pou ki mande gwo vitès lyen seri (eg, PCIe, Gigabit Ethernet, oswa HDMI), konsidere plus modèl FPGA.

5. Ki jan XCV200-6FG456C a konpare ak plus modèl FPGA?

XCV200-6FG456C a ki dwe nan yon jenerasyon ki pi gran nan FPGAs.Konpare ak modèn Virtex FPGAs, li gen yon konte pòtay pi ba, pi dousman vitès revèy, ak efikasite pouvwa limite.Plus modèl ofri pi wo dansite lojik, plis entegre memwa, avanse blòk DSP, ak pi ba konsomasyon pouvwa, fè yo pi bon pou aplikasyon pou modèn.

AD73322AR Pinout, karakteristik, ak detay teknik eksplike

sou 2025/03/21

EP20K100EFC324-1X FPGA: Karakteristik, espesifikasyon, aplikasyon, ak gid pwogramasyon

sou 2025/03/20

Posts popilè

-

Enstriksyon konplèks Set Odinatè: Ki jan yo chanje informatique?

sou 8000/04/18 147770

-

USB-C pinout ak karakteristik

sou 2000/04/18 112002

-

Sèvi ak Xilinx Inifye Simulation Primitif: Yon Gid konplè nan FPGA Design ak Simulation

sou 1600/04/18 111351

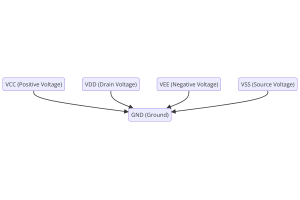

-

Tansyon ekipman pou pouvwa nan elektwonik: siyifikasyon VCC, VDD, VEE, VSS, ak GND

sou 0400/04/18 83768

-

RJ45 Connector Gid: Pinout, fil elektrik, Kalite Kab, ak Itilizasyon

sou 1970/01/1 79561

-

Gid la ultim nan kòd koulè fil nan sistèm elektrik modèn

Fason sistèm elektrik nou yo itilize koulè yo pa sèlman pou sanble.Chak koulè fil kounye a endike yon fonksyon espesifik, fè li pi fasil yo idantifye ak okipe konpozan elektrik kòrèkteman pandan en...sou 1970/01/1 66958

-

Purge Valv Gid: Fonksyon, sentòm, tès, ak ranplasman pou pèfòmans motè optimal

Valv la weteur se yon pati enpòtan nan sistèm yon machin nan ki ede kenbe lè a pwòp pa jere vapè gaz yo anvan yo ka chape anba nan atmosfè a.Sa a pa sèlman ede anviwònman an pa diminye polisyon, me...sou 1970/01/1 63098

-

Kalite (q) Faktè: Ekwasyon ak aplikasyon

Faktè bon jan kalite a, oswa 'Q', se enpòtan lè tcheke ki jan byen endukteur ak rezonan travay nan sistèm elektwonik ki itilize frekans radyo (RF).'Q' mezire ki jan byen yon sikwi minimize pèt enèj...sou 1970/01/1 63040

-

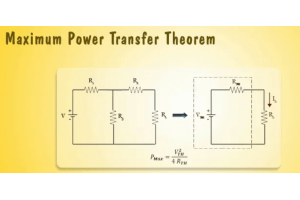

Atenn pèfòmans pik ak teyorèm nan transfè pouvwa maksimòm

Teyorèm maksimòm transfè pouvwa a eksplike kijan enèji ki sòti nan yon sous, tankou yon batri oswa dèlko, ap koule nan yon chaj ki konekte.Li montre kondisyon an egzak kote chaj la resevwa pouvwa k...sou 1970/01/1 54095

-

Espesifikasyon batri A23 ak konpatibilite

Batri a A23 se yon ti, silenn ki gen fòm batri ak vòltaj segondè.Yo te rele tou 23a, 23AE, oswa MN21, li kouri nan 12 vòlt ak pi wo pase AA oswa AAA pil.Konsepsyon espesyal li fè li pafè p...sou 1970/01/1 52182