EPM1270F256C4N MAX II CPLD BECA: Karakteristik, espesifikasyon ak aplikasyon pou

Nan atik sa a, ou pral aprann sou EPM1270F256C4N a, yon CPLD mitan-ranje soti nan fanmi an MAX II pa Altera (kounye a Intel).Nou pral mache nan sa li ye, karakteristik prensipal yo li ofri, ak ki jan dyagram blòk li yo ak I/O bank fè li fleksib pou desen diferan.Ou pral wè tou espesifikasyon li yo, anbalaj, ak modèl CAD.Nou pral kouvri ki jan li te itilize nan aplikasyon pou tankou Otobis Tranzisyon, sistèm psi, kontwòl konfigirasyon, ak sekans pouvwa, osi byen ke etap sa yo nan pwogram li.Finalman, nou pral gade nan avantaj li yo, dezavantaj, ak kèk pati ki sanble pou konparezon.Katalòg

Ki sa ki EPM1270F256C4N a?

A EPM1270F256C4N se yon manm nan fanmi an MAX II nan konplèks aparèy lojik pwogramasyon (CPLDs) devlope pa Altera, kounye a yon pati nan Intel.Li se yon flash ki baze sou, ki pa temèt aparèy ki fèt pou enstantane-sou operasyon, elimine bezwen an pou memwa konfigirasyon ekstèn.Bati sou yon pwosesis flash 0.18 µm, aparèy la entegre resous lojik, konekte, ak entegre memwa flash nan yon solisyon kontra enfòmèl ant ki bay pèfòmans serye ak konsomasyon pouvwa ki ba.Pozisyone nan mitan-ranje a nan fanmi an Max II, EPM1270 a ofri alantou 1,270 eleman lojik, fè li byen adapte pou pwojè ki mande kapasite balanse ak efikasite san yo pa deplase nan pi wo-fen EPM2210 la.Tankou tout aparèy MAX II, li benefisye de nan-sistèm pwogramasyon nan JTAG, multivolt I/O sipò, ak sou-chip itilizatè memwa flash.

Kap chèche EPM1270F256C4N?Kontakte nou yo tcheke stock aktyèl, tan plon, ak prix.

EPM1270F256C4N CAD Modèl

EPM1270F256C4N senbòl

EPM1270F256C4N anprint

EPM1270F256C4N 3D modèl

EPM1270F256C4N karakteristik

• Flash ki baze sou, ki pa Peye-temèt achitekti

Se aparèy la bati sou yon achitekti flash ki baze sou, sa vle di li konsève konfigirasyon li yo san yo pa bezwen an pou memwa ekstèn.Sa a pèmèt pou enstantane-sou fonctionnalités, fè li serye pou sistèm ki dwe kòmanse opere imedyatman apre pouvwa-up.

• Kapasite lojik

EPM1270F256C4N a bay 1,270 eleman lojik (LES) ak sou 980 macrocells, bay ase resous pou mete ann aplikasyon konplèks lojik kontwòl.Sa fè li apwopriye pou aplikasyon pou medyòm-dansite tankou jesyon otobis, koòdone pon, ak kontwòl entegre.

• Pwogramasyon I/O broch

Li sipòte jiska 212 pwogramasyon I/O broch, sa ki pèmèt koneksyon fleksib ak nan yon pakèt domèn interfaces sistèm.Sa a adaptabilite fè li pi fasil entegre ak lòt aparèy ki ka itilize diferan estanda vòltaj.

• Itilizatè Flash memwa (UFM)

Yon blòk entegre 8 Kbit UFM pèmèt depo nan done itilizatè-defini, tankou kle chifreman oswa paramèt konfigirasyon.Karakteristik sa a amelyore sekirite sistèm ak diminye bezwen an pou EEPROM ekstèn.

• High-vitès operasyon

Avèk yon frekans maksimòm de apeprè 304 megaèrts ak reta pwopagasyon osi ba ke 6.2 ns, aparèy la ka okipe tan-kritik fonksyon lojik.Sa a asire pèfòmans lis nan aplikasyon pou gwo vitès tankou pwosesis siyal ak kominikasyon done.

• Multivolt I/O Sipò

CPLD a sipòte plizyè estanda I/O soti nan 1.5 V a 3.3 V, sa ki pèmèt li nan koòdone transparans ak aparèy opere nan tension diferan.Fleksibilite sa a diminye bezwen pou konpozan ekstèn nivo-déplacement.

• Pouvwa efikasite

Aparèy la opere ak kouran ekipman pou tipik alantou 55 Ma, fè li efikas konpare ak pi gran fanmi CPLD.Konsomasyon ba pouvwa estatik li yo ede nan sistèm ki mache ak pil ak enèji-sansib.

• Avanse I/O karakteristik

Li gen ladan bati-an otobis-kenbe rezistans, pwogramasyon rale-ups, entrain Schmitt-deklanche, ak touye-pousantaj kontwòl, ki amelyore estabilite siyal ak tolerans bri.Karakteristik sa yo fè aparèy la gaya lè w ap travay nan melanje-siyal oswa anviwònman fè bwi.

• Nan-sistèm pwogramasyon ak tès la

EPM1270F256C4N a sipòte pwogram JTAG ki baze sou ak konfòm ak IEEE 1532 pou nan-sistèm pwogramasyon.Sipò pou tès-eskanè fwontyè (IEEE 1149.1) asire tès tablo pi fasil ak debogaj pandan manifakti.

• Sipò cho-kou.

Sa a CPLD ka san danje eleman oswa retire nan yon sistèm mache san yo pa sa ki lakòz domaj elektrik.Cho-kou. senplifye antretyen ak amelyorasyon sistèm san yo pa egzije pouvwa-desann.

• Rezo revèy mondyal

Aparèy la bay kat liy revèy mondyal, pèmèt operasyon senkronize atravè etalaj lojik li yo.Sa a asire konsistan distribisyon ak fyab nan aplikasyon pou revèy-entansif tankou kontè, machin eta a, ak contrôleur gwo vitès.

Max II blòk dyagram

Dyagram nan blòk nan aparèy la MAX II, tankou EPM1270F256C4N a, montre ki jan pati prensipal li yo travay ansanm.Nan sant la yo se blòk etalaj lojik (laboratwa), ki gen eleman lojik (LES) ki fè aktyèl fonksyon yo lojik pwogramasyon.Anviwon bor yo se mwen/O eleman (IOES), ki konekte lojik entèn nan broch ekstèn pou kominikasyon ak lòt aparèy.

Pati sa yo lye pa multitrack konekte a, ki aji tankou otowout ki byen vit deplase siyal ant lojik ak I/O blòk.Konfigirasyon sa a fè aparèy la vit, fleksib, ak serye, sa ki pèmèt li okipe travay konplèks pandan y ap rete efikas nan aplikasyon pou mond reyèl la.

EPM1270 I/O Banks

Dyagram nan bank I/O nan EPM1270F256C4N a montre ki jan aparèy la òganize koneksyon opinyon li yo ak pwodiksyon.Se chip la divize an kat I/O bank yo, chak ki antoure nwayo a lojik ak ki kapab sipòte estanda vòltaj miltip tankou 3.3 V, 2.5 V, 1.8 V, ak 1.5 V. Fleksibilite sa a pèmèt aparèy la koòdone ak nan yon pakèt domèn konpozan ekstèn, fè li apwopriye pou sistèm melanje-vòltaj san yo pa egzije chanjman siplemantè nivo.

Yon bank, yo montre kòm I/O Bank 3, tou sipòte 3.3 V estanda a PCI, pèmèt konpatibilite ak eritaj PCI ki baze sou desen.Pa separe broch nan bank yo, ou ka bay nivo vòltaj diferan nan diferan gwoup, ki amelyore entegrasyon sistèm ak opsyon konsepsyon tablo.Estrikti sa a enpòtan paske li bay EPM1270F256C4N kapasite a yo aji kòm yon kontwolè santral nan sistèm konplèks, manyen estanda siyal divès pandan y ap kenbe pèfòmans serye.

EPM1270F256C4N Espesifikasyon

|

Lèt |

Paramèt |

|

Fabrikan |

Altera/Intel |

|

Seri |

Max® II |

|

Anbalaj |

Plato |

|

Estati pati |

Aktif |

|

Kalite pwogramasyon |

Nan sistèm pwogramasyon |

|

Reta tan TPD (1) Max |

6.2 ns |

|

Pwovizyon pou vòltaj - Entèn |

2.5V, 3.3v |

|

Kantite eleman lojik/blòk |

1270 |

|

Kantite macrocells |

980 |

|

Kantite I/O |

212 |

|

Tanperati opere |

0 ° C ~ 85 ° C (TJ) |

|

Kalite aliye |

Sifas mòn |

|

Pake / Ka |

256-BGA |

|

Pake aparèy founisè |

256-FBGA (17x17) |

|

Nimewo pwodwi baz |

EPM1270 |

EPM1270F256C4N aplikasyon

1. Otobis Tranzisyon ak koòdone Tranzisyon

EPM1270F256C4N a se lajman itilize pou pon ant otobis diferan oswa pwotokòl kominikasyon.Avèk bank fleksib I/O li yo ki sipòte plizyè estanda vòltaj, li ka konekte aparèy modèn nan sistèm eritaj san yo pa konvètisè ekstèn.Sa fè li itil nan anviwònman melanje-teknoloji kote konpatibilite ki nesesè.

2. PCI BUS Sib oswa repeteur

Sa a CPLD ka aji kòm yon sib 32-bit psi nan 66 megaèrts oswa sèvi kòm yon repeater sou sistèm backplane.Pa sipòte estanda a 3.3 V PCI, li asire konfòmite ak desen ki pi gran pandan y ap toujou opere avèk efikasite nan dispozisyon plus.Kapasite sa a fè li yon chwa serye nan ankadreman entegre ak contrôleur endistriyèl.

3. Otobis lakòl lojik ak adrès dekodaj

Anpil souvan itilize EPM1270F256C4N a aplike lojik lakòl ki konekte subsistèm yo ansanm.Gwo kantite eleman lojik li yo kapab tou okipe adrès dekodaj, diminye bezwen an pou plizyè bato disrè.Sa a pa sèlman senplifye konsepsyon sikwi, men tou ekonomis espas ak pri sou PCB la.

4. Jesyon konfigirasyon ak flash loader

Aparèy la se kapab nan jere konfigirasyon FPGA, souvan aji kòm yon loader flash JTAG.Li ka magazen done konfigirasyon ak dirèkteman pwogram FPGAs, diminye kondisyon memwa ekstèn.Sa fè li gen anpil valè nan sistèm ki mande pou fleksib oswa milti-aparèy konfigirasyon manyen.

5. Pouvwa-sou Reyajiste ak Sekans Kontwòl

EPM1270F256C4N a byen adapte pou kontwole siyal reset ak sekans sistèm pouvwa-up.Li asire ke eleman inisyalize nan lòd ki kòrèk la, amelyore fyab pandan demaraj.Anpil sèvi ak li pou kontwòl sipèvize yo anpeche erè ki te koze pa kondisyon pouvwa enstab.

6. I/O ekspansyon ak depo ki pa temèt

Avèk plis pase 200 I/O broch, aparèy la ka sèvi kòm yon ekspansyon I/O nan sistèm ki bezwen plis koneksyon.Li bati-an 8 Kbit itilizatè Flash memwa pèmèt depo nan paramèt, done konfigirasyon, oswa kle chifreman san yo pa EEPROM ekstèn.Karakteristik sa a ajoute fleksibilite ak sekirite pandan y ap diminye konte eleman.

EPM1270F256C4N Pati ki sanble

|

Spesifikasyon |

EPM1270F256C4N |

EPM1270F256C3N |

EPM1270F256C5N |

EPM1270F256I5N |

EPM1270F256C3ES |

EPM1270F256C4

|

|

Eleman lojik (les) |

1,270 |

1,270 |

1,270 |

1,270 |

1,270 |

1,270 |

|

Macrocells |

~ 980 |

~ 980 |

~ 980 |

~ 980 |

~ 980 |

~ 980 |

|

Mwen/o broch |

Jiska 212 |

Jiska 212 |

Jiska 212 |

Jiska 212 |

Jiska 212 |

Jiska 212 |

|

Itilizatè Flash memwa (UFM) |

8 Kbits |

8 Kbits |

8 Kbits |

8 Kbits |

8 Kbits |

8 Kbits |

|

Pakèt |

256-FBGA |

256-FBGA |

256-FBGA |

256-FBGA |

256-FBGA |

256-FBGA |

|

Vitès |

C4 (estanda) |

C3 (pi vit) |

C5 (pi wo) |

I5 (Endistriyèl) |

C3ES (pi vit) |

C4 (estanda) |

|

Max Freq.(MHz) |

~ 304 |

~ 304 |

~ 304 |

~ 304 |

~ 304 |

~ 304 |

|

Pwopagasyon reta |

~ 6.2 ns |

~ 6.2 ns |

~ 6.2 ns |

~ 6.2 ns |

~ 6.2 ns |

~ 6.2 ns |

|

Temp.Distans |

0 a 70 ° C |

0 a 70 ° C |

0 a 85 ° C |

–40 a +85 ° C |

0 a 70 ° C |

0 a 70 ° C |

|

Sèvi ak fòs ka |

Jeneral |

Pi wo vitès |

Endistriyèl/Hi |

Rezistan/piman bouk |

Dev/tès vit |

Alt ekivalan |

EPM1270F256C4N etap pwogramasyon

Anvan ou ka itilize EPM1270F256C4N a, ou bezwen pwogram li ak konsepsyon ou.Pwosesis la se senp si ou swiv chak etap ak anpil atansyon lè l sèvi avèk zouti yo apwopriye ak lojisyèl.

1. Prepare zouti ou yo ak koneksyon pyès ki nan konpitè

Ou kòmanse pa mete kanpe anviwònman an pyès ki nan konpitè.Konekte tablo CPLD ou a nan yon PC lè l sèvi avèk yon pwogramè JTAG konpatib, tankou yon USB-Blaster oswa ByteBlaster II kab.Asire ke aparèy la gen pouvwa ki estab ak broch yo JTAG (TDI, TDO, TCK, ak TMS) yo kòrèkteman konekte.Sa a asire ke sistèm ou an pare pou kominikasyon anvan pwogramasyon an.

2. jenere dosye a pwogramasyon

Next, ou itilize lojisyèl an Quartus II konpile konsepsyon ou ak kreye yon dosye pwogramasyon.Fòma a dosye komen se POF (dosye objè pwogramè), men ou ka kreye tou konfiti (.jam) oswa JBC (.jbc) dosye si ou bezwen yo pou otomatik oswa entegre pwogramasyon.Pa génération dosye sa a, ou bezwen pake konsepsyon lojik ou pou li ka chaje nan CPLD la.

3. Configured pwogramè a Quartus

Louvri zouti nan pwogramè Quartus epi chwazi pyès ki nan konpitè JTAG konekte ou nan opsyon yo konfigirasyon.Lè sa a, chaje dosye a POF, konfiti, oswa JBC ou te kreye nan etap anvan an.Lojisyèl la pral otomatikman detekte aparèy la CPLD sou chèn lan JTAG, epi ou dwe chwazi li pou pwogramasyon.Etap sa a prepare zouti a pou kominike dirèkteman ak chip la.

4. Pwogram konfigirasyon memwa a flash (CFM)

Koulye a, ou ka kòmanse pwogramasyon aparèy la.Pwogramè a Quartus transfere konsepsyon ou nan memwa konfigirasyon aparèy la (CFM), ki pèmanan magazen lojik ou.Yon fwa pwograme, aparèy la pral otomatikman chaje konsepsyon an nan pouvwa-up, pran avantaj de enstantane-sou li yo achitekti flash.Sa a asire sistèm ou an kòmanse opere imedyatman apre Reyajiste oswa pouvwa monte bisiklèt.

5. Pèmèt an tan reyèl nan-sistèm pwogramasyon (si ou vle)

Si ou vle mete ajou CPLD a san yo pa kanpe operasyon li ye kounye a, ou ka pèmèt an tan reyèl ISP.Karakteristik sa a pèmèt ou pwogram yon nouvo imaj konsepsyon nan memwa flash pandan y ap aparèy la ap kontinye kouri.Nouvo konsepsyon an pral sèlman pran efè apre reset nan pwochen oswa sik pouvwa.Li nan espesyalman itil nan sistèm ki dwe rete operasyonèl pandan dènye.

6. Aplike kranpon ISP si sa nesesè (si ou vle)

Pandan pwogramasyon an, ou ka bezwen sèten broch I/O pou rete estab.Nan ka sa yo, ou ka itilize karakteristik nan kranpon ISP fòse broch nan eta segondè, ki ba, oswa kenbe pandan pwogramasyon.Sa a anpeche latwoublay sou siyal pandan y ap chip a ke yo te mete ajou.Li asire sekirite sistèm lè pwogramasyon nan anviwònman ap viv la.

7. Sèvi ak dosye konfiti/JBC pou automatisation (si ou vle)

Pou aplikasyon entegre oswa dispozisyon tès otomatik, ou ka itilize konfiti oswa dosye JBC olye pou yo dirèkteman chaje yon POF.Dosye sa yo ki baze sou script ak pèmèt ou otomatize travay pwogramasyon nan contrôleur ekstèn.Pa fè sa, ou ka jere dènye CPLD nan liy pwodiksyon oswa sistèm jaden san yo pa bezwen Quartus sou yon PC.

8. Pwogram itilizatè a memwa flash (si ou vle)

Aparèy la gen ladan tou yon 8 Kbit itilizatè Flash memwa (UFM) blòk pou ki pa Peye-temèt done itilizatè.Ou ka pwogram sa a separeman nan magazen atik tankou anviwònman konfigirasyon, kle chifreman, oswa done kalibrasyon.Depi UFM se endepandan de lojik prensipal la, ou ka mete ajou li san yo pa afekte konsepsyon an pwograme.Sa fè chip itil pou sekirite ak sistèm personnalisation.

9. Verifye epi teste aparèy la

Apre pwogramasyon an, li enpòtan pou verifye pwosesis la.Quartus otomatikman fè yon chèk verifikasyon, men ou ta dwe tou teste lojik sistèm ou a konfime li konpòte li jan yo espere a.Konsepsyon an ap kòmanse kouri imedyatman apre pwogramasyon, ban nou fidbak enstantane.Etap sa a asire fyab anvan ou deplase nan deplwaman konplè.

10. rkonfigurasyon oswa mete ajou jan sa nesesè

Apre yon tan, ou ka bezwen amelyore oswa chanje konsepsyon ou.Pou fè sa, tou senpleman rejenerasyon yon nouvo POF nan Quartus ak repete pwosesis la pwogramasyon.Ou kapab tou itilize ISP oswa konfiti Scripts pou dènye nouvèl sou douser san D 'sistèm.Fleksibilite sa a fè EPM1270F256C4N pratik pou pwojè en.

EPM1270F256C4N avantaj ak dezavantaj

Avantaj

• pri ki ba konpare ak pi gran CPLDs ak aparèy menm jan an.

• Konsomasyon pouvwa ki ba anpil, ideyal pou sistèm efikas.

• Pi wo pèfòmans ak dansite pase fanmi Max anvan yo.

• Ki pa Peye-temèt, enstantane-sou demaraj san yo pa memwa ekstèn.

• Redwi konpozan ekstèn, ekonomize espas PCB ak pri.

Dezavantaj

• Limite kapasite lojik konpare ak FPGA modèn.

• manke blòk avanse tankou DSPs oswa resèpteur gwo vitès.

• Pi wo pri pou chak-inite pase ASICs nan komèsan trè wo.

• Mande pou zouti HDL ak konesans pwogramasyon.

• Achitèk fiks limite fleksibilite nan routage konplèks.

EPM1270F256C4N dimansyon anbalaj

|

Lèt |

Paramèt |

|

Kalite pake |

256-FBGA (17 × 17 mm) |

|

Dimansyon d (kò) |

17.0 mm |

|

Dimansyon E (kò) |

17.0 mm |

|

Boul boul (e) |

1.0 mm |

|

Dyamèt boul (b) |

0.60 mm |

|

An jeneral wotè (a) |

1.70 mm (max) |

|

Wotè kanpe (A1) |

0.25 mm (min) |

|

Pake epesè (A2) |

1.35 mm (tip) |

|

Epesè substrate (A3) |

0.25 mm (tip) |

|

PIN Idantifikatè A1 |

Mak kwen (Top View) |

EPM1270F256C4N manifakti

EPM1270F256C4N a manifaktire pa Altera, yon konpayi rekonèt pou lidèchip li yo nan aparèy lojik pwogramasyon, patikilyèman CPLDs ak FPGAs.Te fonde an 1983, Altera te vin yon pyonye nan teknoloji pwogramasyon semi-conducteurs ak bati yon repitasyon fò pou fournir inovatè, pri-efikas, ak pèfòmans-wo solisyon lojik.Nan 2015, Altera te rann pa Intel Corporation, entegre liy pwodwi li yo nan gwoup solisyon pwogramasyon Intel la.Jodi a, fanmi an Max II, ki gen ladan EPM1270F256C4N a, kontinye ap sipòte ak distribye anba mak la Intel, konbine eritaj Altera a nan ekspètiz lojik pwogramasyon ak echèl mondyal Intel a, avanse fabrikasyon semi-conducteurs, ak fyab alontèm nan ekipman pou.

Konklizyon

EPM1270F256C4N a ofri enstantane-sou, flash ki baze sou pwogramasyon ak kapasite lojik balanse, ki ba pouvwa itilize, ak gwo sipò I/O vòltaj.Li bay operasyon serye pou Tranzisyon, lojik lakòl, kontwòl sistèm, ak I/O ekspansyon pandan y ap ki gen ladan opsyon tankou itilizatè memwa flash ak nan-sistèm pwogramasyon.Malgre ke li gen mwens resous pase FPGA modèn ak manke fonksyon avanse tankou blòk DSP, li fè moute pou sa a ak pi ba pri, senplisite, ak bezwen redwi pou eleman siplemantè.An jeneral, li se yon chwa fò pou entegre ak sistèm endistriyèl ki bezwen efikasite, fleksibilite, ak pèfòmans serye.

Fich pdf

EPM1270F256C4N FACASHEETS:

Sou nou

ALLELCO LIMITED

Li piplis

Quick Inquiry

Tanpri voye yon ankèt, nou pral reponn imedyatman.

Kesyon yo poze souvan [FAQ]

1. Èske EPM1270F256C4N a dwe itilize nan sistèm ki mache ak pil?

Wi, ak ba li yo konsomasyon pouvwa estatik ak efikas flash ki baze sou konsepsyon, li se byen adapte pou pòtab oswa batri ki mache ak aplikasyon ki mande pou disponiblite san yo pa seche enèji.

2. Èske EPM1270F256C4N a mande pou memwa ekstèn pou operasyon?

Non, youn nan avantaj prensipal li yo se konsepsyon flash ki baze sou li yo ki pa temèt, ki retire bezwen an pou yon memwa konfigirasyon ekstèn, diminye konte eleman ak espas tablo.

3. Èske EPM1270F256C4N konpatib ak sistèm Legacy PCI?

Wi, aparèy la sipòte estanda a 3.3 V PCI, sa ki pèmèt li konekte ak pi gran sistèm PCI ki baze sou pandan y ap toujou kenbe konpatibilite ak modèn anviwònman melanje-vòltaj.

4. Èske EPM1270F256C4N a dwe mete ajou pandan y ap kouri nan yon sistèm?

Wi, li sipòte nan-sistèm pwogramasyon (ISP), sa vle di dènye ka chaje nan memwa flash pandan y ap aparèy la ap kontinye opere, minimize sistèm D '.

5. Ki sa ki fè EPM1270F256C4N a plis serye pase pi gran CPLDs?

Konsepsyon enstantane-sou flash li yo, avanse I/O karakteristik tankou otobis-kenbe rezistans ak entrain Schmitt-deklanche, ak cho-sipòte sipò tout kontribye nan pi wo fyab ak entegrasyon pi an sekirite.

LFEC3E-3Q208C FPGA Apèsi sou lekòl la: Karakteristik, aplikasyon, pwogramasyon, ak espesifikasyon

sou 2025/08/28

TMS320C6421ZWT5 DSP Apèsi sou lekòl la: karakteristik, altènativ, espesifikasyon, ak aplikasyon pou

sou 2025/08/26

Posts popilè

-

Enstriksyon konplèks Set Odinatè: Ki jan yo chanje informatique?

sou 8000/04/19 147782

-

USB-C pinout ak karakteristik

sou 2000/04/19 112065

-

Sèvi ak Xilinx Inifye Simulation Primitif: Yon Gid konplè nan FPGA Design ak Simulation

sou 1600/04/19 111352

-

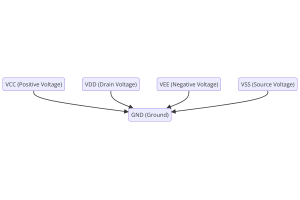

Tansyon ekipman pou pouvwa nan elektwonik: siyifikasyon VCC, VDD, VEE, VSS, ak GND

sou 0400/04/19 83824

-

RJ45 Connector Gid: Pinout, fil elektrik, Kalite Kab, ak Itilizasyon

sou 1970/01/1 79639

-

Gid la ultim nan kòd koulè fil nan sistèm elektrik modèn

Fason sistèm elektrik nou yo itilize koulè yo pa sèlman pou sanble.Chak koulè fil kounye a endike yon fonksyon espesifik, fè li pi fasil yo idantifye ak okipe konpozan elektrik kòrèkteman pandan en...sou 1970/01/1 67004

-

Purge Valv Gid: Fonksyon, sentòm, tès, ak ranplasman pou pèfòmans motè optimal

Valv la weteur se yon pati enpòtan nan sistèm yon machin nan ki ede kenbe lè a pwòp pa jere vapè gaz yo anvan yo ka chape anba nan atmosfè a.Sa a pa sèlman ede anviwònman an pa diminye polisyon, me...sou 1970/01/1 63128

-

Kalite (q) Faktè: Ekwasyon ak aplikasyon

Faktè bon jan kalite a, oswa 'Q', se enpòtan lè tcheke ki jan byen endukteur ak rezonan travay nan sistèm elektwonik ki itilize frekans radyo (RF).'Q' mezire ki jan byen yon sikwi minimize pèt enèj...sou 1970/01/1 63067

-

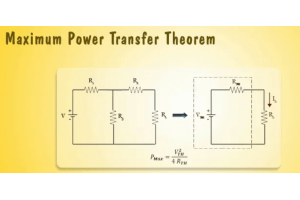

Atenn pèfòmans pik ak teyorèm nan transfè pouvwa maksimòm

Teyorèm maksimòm transfè pouvwa a eksplike kijan enèji ki sòti nan yon sous, tankou yon batri oswa dèlko, ap koule nan yon chaj ki konekte.Li montre kondisyon an egzak kote chaj la resevwa pouvwa k...sou 1970/01/1 54097

-

Espesifikasyon batri A23 ak konpatibilite

Batri a A23 se yon ti, silenn ki gen fòm batri ak vòltaj segondè.Yo te rele tou 23a, 23AE, oswa MN21, li kouri nan 12 vòlt ak pi wo pase AA oswa AAA pil.Konsepsyon espesyal li fè li pafè p...sou 1970/01/1 52218